工具/软件:

您好的团队、

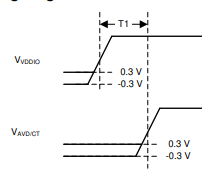

在客户的 持续设计中、 通过为 AVD 供电的 3.3V 电压产生了 2.5V 的 VDDIO 电压。

因此、在 VDDIO 完全斜升之前、不可能等待 AVD 斜升。

因此、我的客户想知道当 VDDIO<VDDIO+0.3V 时是否允许使用 AVD。

请检查一下。

如果不建议这样做、请告知如何解决?

此致、

伊藤和树

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

您好的团队、

在客户的 持续设计中、 通过为 AVD 供电的 3.3V 电压产生了 2.5V 的 VDDIO 电压。

因此、在 VDDIO 完全斜升之前、不可能等待 AVD 斜升。

因此、我的客户想知道当 VDDIO<VDDIO+0.3V 时是否允许使用 AVD。

请检查一下。

如果不建议这样做、请告知如何解决?

此致、

伊藤和树

尊敬的伊藤山:

因此、我的客户想知道 VDDIO 时是否允许这样做 我认为不建议这样做、因为可能会发生误检。 当 AVD 完成斜升并在 该电源轨仍在斜升时对 VDDIO 电压进行采样时、会发生错误检测。 在这种情况下、PHY 可能会 在电源轨完成斜升之前错误地读取 VDDIO 电压。

作为权变措施、客户是否可以为 VDDIO 使用 3.3V 电压? 如果不能这样做、我建议同时升高 VDDIO 和 AVD(如果可以这样做)。

请告诉我您的想法。

此致、

j

尊敬的 J:

我有客户的几个问题。

此致、

伊藤和树

尊敬的 J:

关于#2、 是的、初始有 1V 斜坡、但仍在 数据表中指定的 t1=±100ms 范围内。 不允许吗?

关于#3、我的客户正在转至 Table 10-1 Power Supply Characteristics(表 10-1 电源特性)。 但是、我的客户想在 VDDIO=2.5V 和 AVD =3.3V 下提供数据。 有道理吗?

此致、

Kazuki Ioth

尊敬的伊藤山:

以下是 VDDIO 2.5V 和 AVD 3.3V 的功率测量结果。

如果您对此有任何疑问、敬请告知。

e2e.ti.com/.../DP83822_5F00_Power_5F00_Measurement.xlsx

此致、

j