工具/软件:

我们设计了一个结合使用 TMDS1204 和 AMD FPGA 的 HDMI 输入/输出板。

HDMI 合规性测试由 HDMI 认证机构执行、并发现以下故障。

1 号输出测试 ID 7-4 TMDS - Trise、Tfall

当输出 3840x2160@30p 信号时、Data0、Data1 和 Data2 的上升和下降时间小于 70ps、而规格为 75ps 或更高。

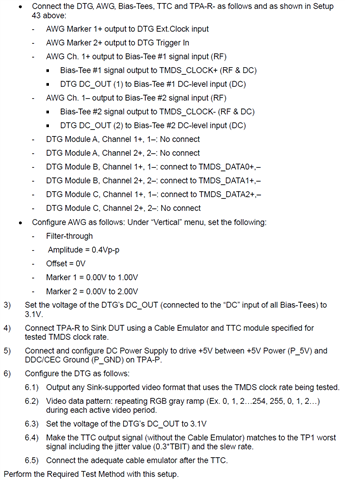

从 TMDS1204 数据表中、我认为可以通过更改 SLEW_3G_Register 设置来处理此问题、我是否正确?

如果可能、请告诉我您在输出 3840x2160@30p 时、SLEW_3G_Register 设置的更改会改变上升和上升时间的评估结果。

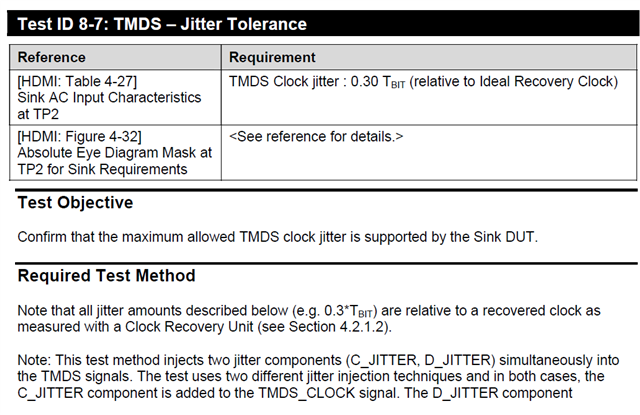

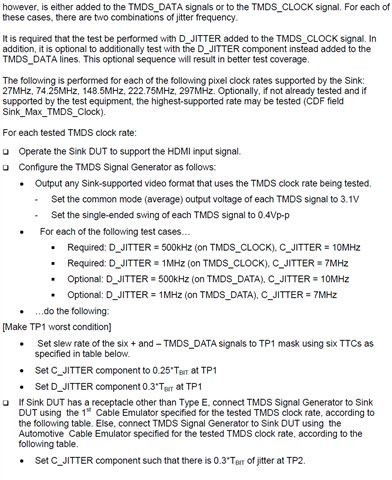

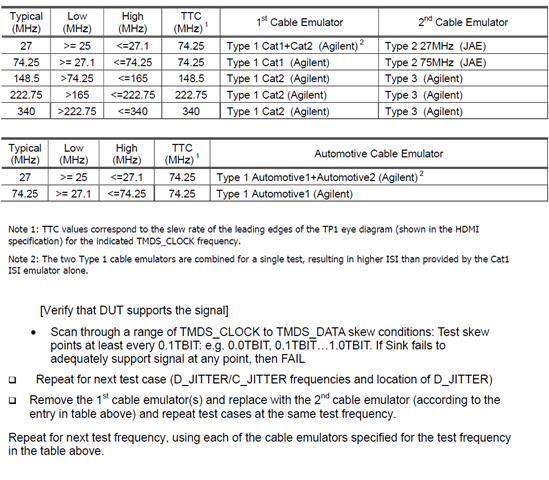

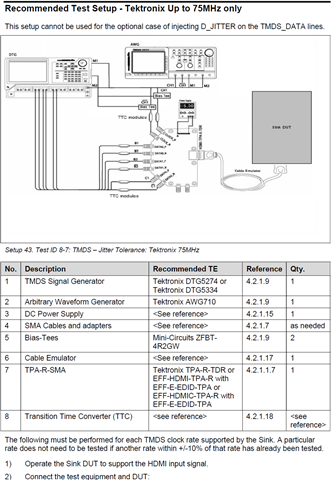

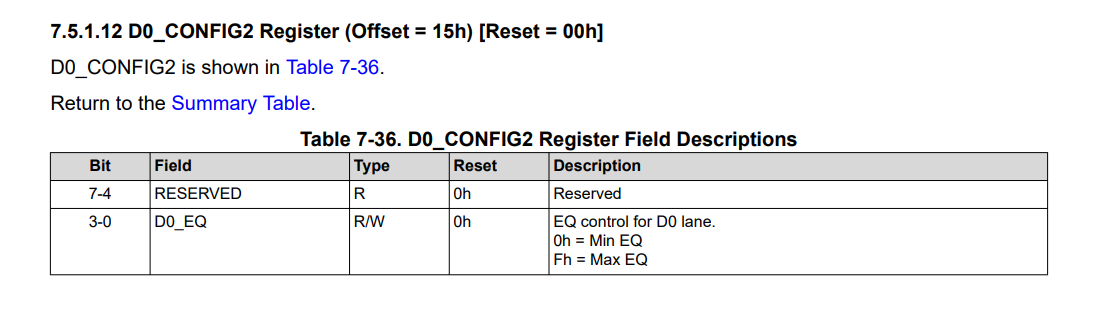

2 号输入测试 ID 8-7:TMDS –抖动容差

只有 27M Type 2 27MHz (JAE) 配置失败、27M Type 1 Cat1+Cat2 (Agilent) 配置 和 74M、148M、222M、297M 通过。

最初、我认为 FPGA 缺少抖动容限、因此我联系了 AMD、但他们向我保证、如果没有使用转接驱动器清除抖动、FPGA 将无法接收数据。

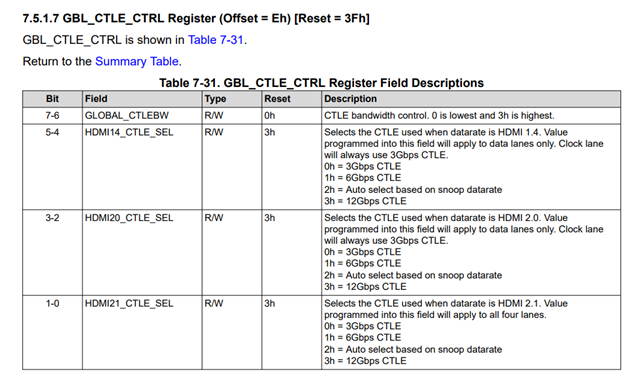

我参考了数据表、但找不到合适的设置来在低传输速率下提高抖动容差。 请让我知道该尝试什么。