Other Parts Discussed in Thread: DS90LV011A, DS90LV012A, DS90LV011-12AEVM

主题中讨论的其他器件: DS90LV012A、 DS90LV011-12AEVM

工具/软件:

尊敬的 TI 团队:

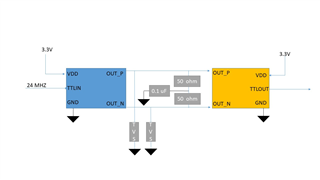

我们的工程使用了 DS90LV011A+DS90LV012A 来提供 24M Hz CLK 输入。

模拟了 DS90LV011A 设计。 但我们发现、当器件开启时、屏幕会闪烁。

曾尝试在 GND 上添加 47pF 电阻、并在 TTL IN 引脚中添加 56 Ω 串联电阻。

问题已得到改善、但尚未完全解决。

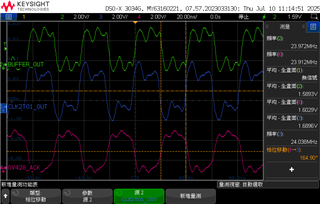

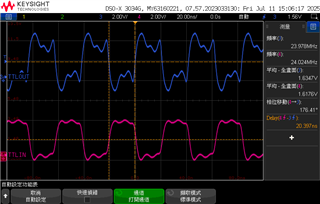

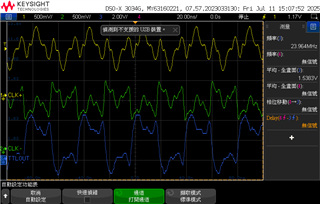

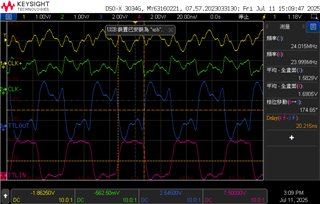

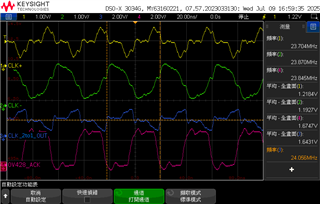

TTLIN、OUT+/-、TTLOUT 波形为爆炸值。

TTLOUT 似乎已衰减。

请帮助回答这些问题~

1.如何解决这个问题?

DS90LV011A 是否可以调节驱动?

3. TTLIN +OUT/-+ TTLOUT 总共有多远?

(使用 DS90LV011-12AEVM 进行实验。 它也有同样的问题。)

谢谢~

此致、

Andy