Other Parts Discussed in Thread: TDP0604, SN65DP159, DP159RGZEVM, TDP0604EVM

主题中讨论的其他器件: SN65DP159、 DP159RGZEVM、

工具/软件:

您好 TI

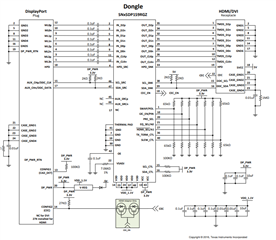

我们的应用程序在附带的计算机主板上使用英特尔处理器。

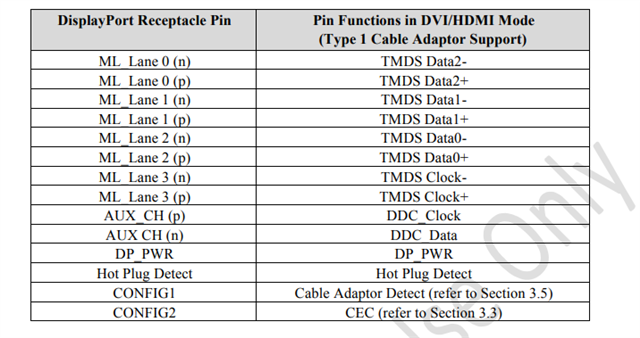

我们使用 DDI 作为监视器输出。 计算机模块的数据表指定 DDI 支持 DP++。

我们希望将视频输出到外部 DVI 显示器。

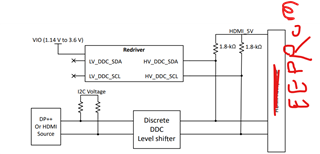

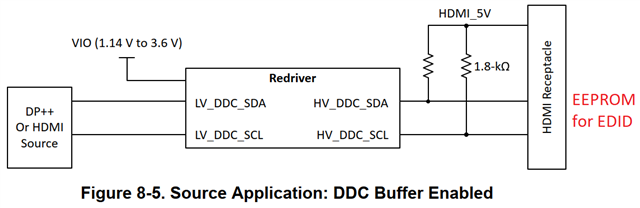

但是、外部显示器不支持 DDC 接口、但固定了已知分辨率。

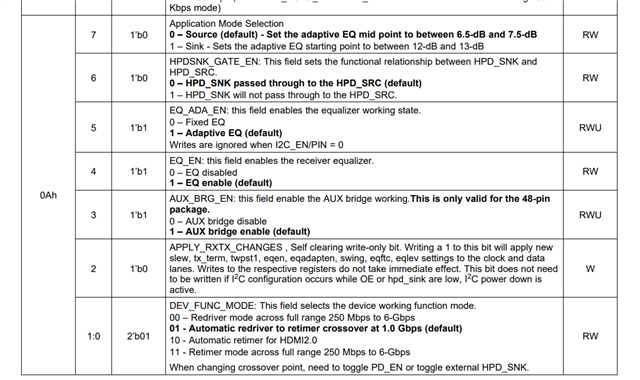

在这种情况下是否可以使用 TDP0604 或 SN65DP159? 是否需要 DDC 接口?

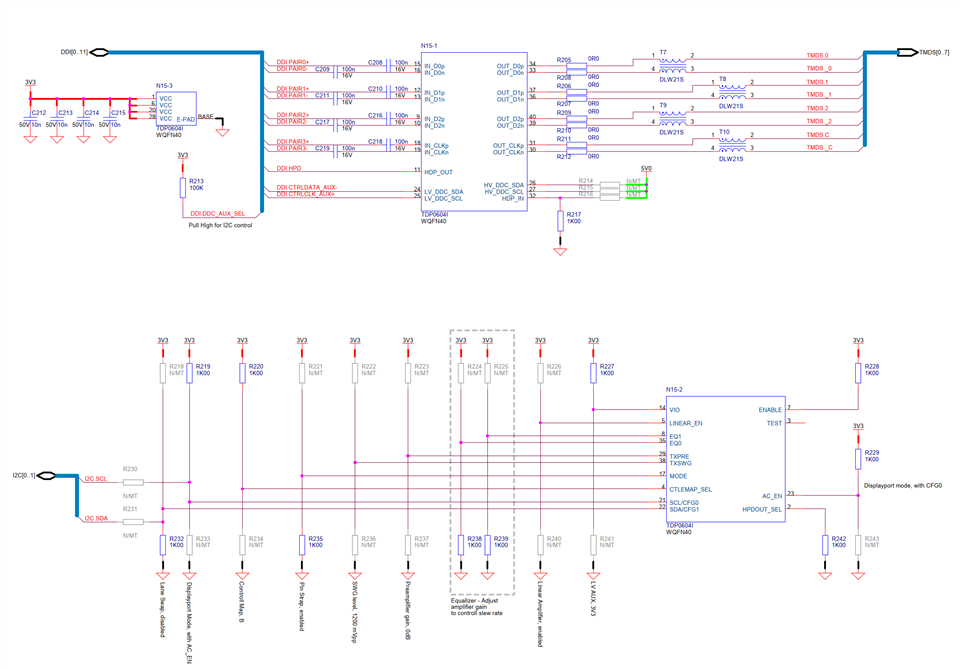

另外、应该如何将交流和直流输入和输出进行耦合?

我们目前有一种使用 TDP0604 的实现方案 、该方案具有交流耦合输入和直流耦合输出、此设置目前无法正常使用。

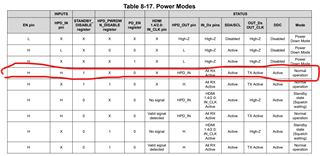

我们打算在搭接模式下使用 TDP0604。

我们尝试在 HPD_IN 上添加一个连接到 5V 的上拉电阻器但没有成功。

您能帮助我们更接近解决方案吗?

此致

Lars