工具/软件:

您好:

我们使用了 DP83867CRRGZ、但有时连接会下降、比方说是随机的。

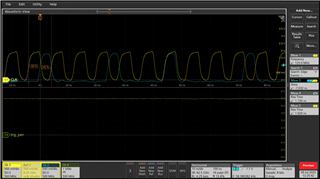

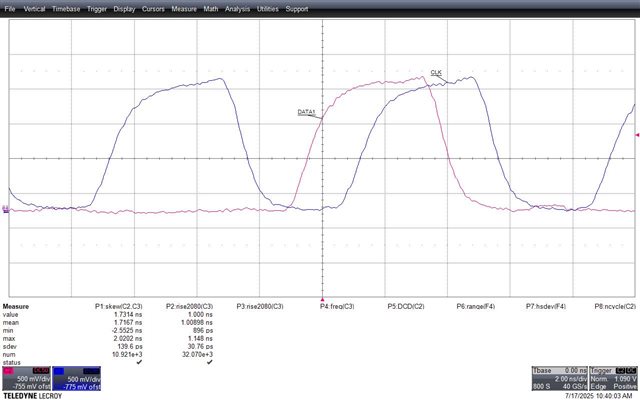

首先、我们通过示波器和 Z0 探头 (焊接在 DP83867CRRGZ 附近的 TX 侧电线上)检查 RGMII CLK 和数据。 这种方法是否可以获得良好的测量结果?

CLK 和数据信号在我们的 PCB 上是长度匹配的 — 皮秒差异。

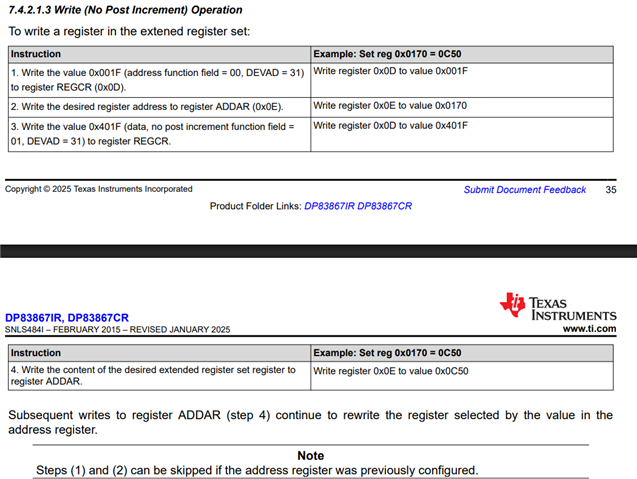

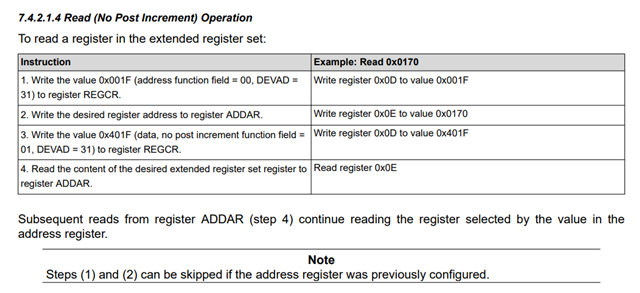

我想输出的信号是错误的、我们需要通过 0x0086 寄存器正确设置延迟、但我不确定、我很乐意再次检查 此问题。

蓝色波为 CLK、红色数据信号。

非常感谢您对如何解决我们的问题的任何想法。

Tomas