工具/软件:

尊敬的专家

音响主机和通过 FPD-link 进行的屏幕通信。 串行器为 DS90UB941、解串器为 DS90UB948。

在 EMC RE 测试中、以下频率点超出了限制值。

400MHz、450MHz 和 845MHz。

音响主机上的频谱分析仪超出了 DS90UB941 和 DS90UB947 之间 FPD-Link 的噪声。

问题:是否可以通过软件调整 FPD-link 驱动强度? 如果是、哪些寄存器控制该设置?

谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具/软件:

尊敬的专家

音响主机和通过 FPD-link 进行的屏幕通信。 串行器为 DS90UB941、解串器为 DS90UB948。

在 EMC RE 测试中、以下频率点超出了限制值。

400MHz、450MHz 和 845MHz。

音响主机上的频谱分析仪超出了 DS90UB941 和 DS90UB947 之间 FPD-Link 的噪声。

问题:是否可以通过软件调整 FPD-link 驱动强度? 如果是、哪些寄存器控制该设置?

谢谢!

尊敬的客户:

感谢您的提问。

一些数据将帮助我们更好地为您提供支持:

问题:是否可以通过软件调整 FPD-link 驱动强度? 如果是、哪些寄存器控制此设置?

关于您的问题、降低 VOD 将有助于提高 RE 性能。 不过、我们所有器件测试和验证都是在默认 VOD 设置下完成的。

我建议客户执行自己的验证和应力测试、以确保较低的 VOD 设置对于其应用来说是稳健的。

以下是修改 VOD 的过程。 (默认 VOD =1.1Vppk、新设置=0.8Vppk):

谢谢、

Ragav Subramanian

你好 Ragav

感谢您的反馈。

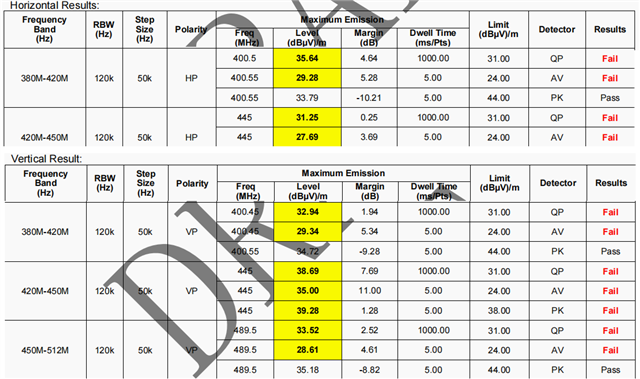

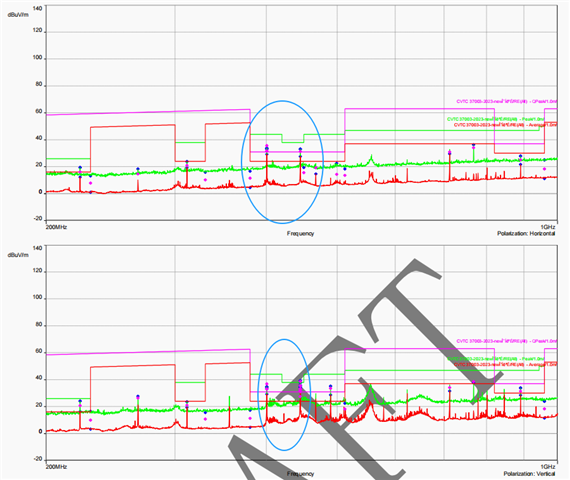

1.下表是 RE 数据

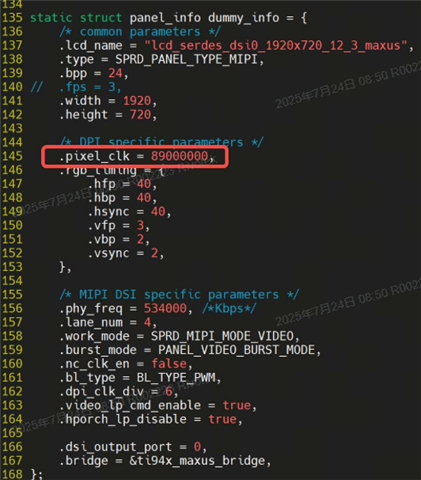

2. screnn 的 PCLK 为 89MHz

3.这里有两个问题。

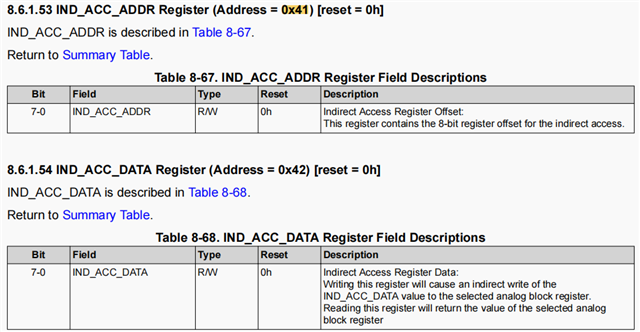

(1) 一个是关于您的注册建议。 我研究了 DS90UB941 规范寄存器。 这些寄存器似乎与 VOD 电平无关?

(2) 关于 445MHz 处的噪声点、它是 PCLK 频率的 5 倍。 PCLK 是否是 445MHz 噪声点的噪声源?

顺便说一下、当 DS90UB941 关闭时、445MHz 和 400MHz 噪声点消失。

谢谢!

您好、

您能否分享客户名称和项目以获取我们的记录?

[引述 userid=“639423" url="“ url="~“~/support/interface-group/interface/f/interface-forum/1543846/ds90ub941as-q1-how-to-adjust-the-drive-strength-of-fpd-link-of-ds90ub941/5940859 ](2) 关于 445MHz 处的噪声点、它是 PCLK 频率的 5 倍。 PCLK 是否会成为 445MHz 噪声点的噪声源?根据该数据、两个失败频率是 400MHz 和 445MHz。 如您所述、445MHz 尖峰可能是 PCLK 的谐振频率、达到奈奎斯特频率的 5 倍。 400MHz 不会成为 PCLK 的谐波、这很有趣。

顺便说一下、当 DS90UB941 关闭时、445MHz 和 400MHz 噪声点消失。

这是一项很好的测试、可以验证发射源。 解串器是否也已关闭?

我们需要确定 RE 是与串行器还是解串器相关、以及它是否取决于 PCLK。

我会尝试两件事:

| 串行器 | 子系统 | 通过/未通过 |

| 已断电 | 已断电 | ??? |

| 上电、PDB 保持低电平 | 上电、PDB 保持低电平 | ??? |

| 通过 DES 侧的 FPD 终端进行上电 | 上电、PDB 保持低电平 | ??? |

| 上电、PDB 保持低电平 | 已通电并在串行器侧使用 FPD 终端 | ??? |

用于控制 VOD 的寄存器位于间接寄存器页面上、我们的数据表中不会公开该寄存器。 寄存器 0x41-0x42 控制对这些间接寄存器的访问。 请遵循之前提供的配方、并验证示波器上的输出变化。

谢谢、

Ragav Subramanian