请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:TXB0104主题中讨论的其他器件: LSF0204、 TXU0304、TXU0104、TXU0204

工具/软件:

您好、

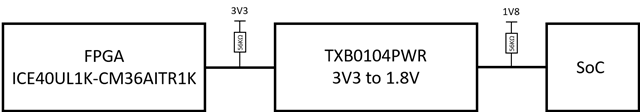

我将使用电平转换器器件 TXB0104PWR 在我的设计中、将 FPGA (3.3V) 与 SoC (1.8V) 连接起来。

以下是设置:

- FPGA 输出 A 复位 信号、该信号为开漏并被上拉至 3.3V 使用 56kΩ 电阻器 。

- 此复位信号连接到 3.3V 侧 转换器 (VCCB) 的转换时间。

- 。 1.8V 侧 电平转换器的 (VCCA) 连接到 SoC、也上拉至 1.8V 连接 56kΩ 电阻器 。

- FPGA 经过编程、可始终保持在 3.3V、为 SoC 供电

- 当 FPGA 驱动为低电平时、SoC 保持复位状态、并将继续 关闭电源 。

我已经确认 FPGA 和 SoC 可单独正常工作。 但是、RESET 逻辑无法在系统中按预期运行、并且 SoC 不会退出复位。 这表明这种开漏设置中的电平转换器行为存在潜在问题。 电平转换器是否采用了正确的配置? 请告诉我、在此类开漏驱动电路中、是否需要了解任何其他配置要求或限制。