工具/软件:

我们使用 SN65DSI86 产品、它在通电时能正常显示、并且屏幕长时间保持打开状态。 使用一段时间后(可能 30 分钟、可能 3 小时或更长时间)、屏幕突然变黑、背光正常。 我是否可以询问如何解决这种情况、需要读取哪些寄存器来找到问题、或者需要测量哪些信号?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

嗨、Haibin、

对于这种情况、我建议执行以下过程:

器件中有多个可用的诊断寄存器、可帮助确定运行时哪个功能(输入/输出协议)出现问题。

通过对这两个日志进行直接比较、可以了解哪些配置可以轻松更改、以及需要重点关注哪些配置。

下面是一个示例脚本:

e2e.ti.com/.../RegisterDumpExample.py

您是否还能在测试期间提供任何其他条件(如果有)?

谢谢、

Miguel

e2e.ti.com/.../Black.csve2e.ti.com/.../OK.csv

附件 OK.csv 在正常显示时显示转储信息、而 black.csv 在屏幕黑屏时显示转储信息。

sn65dsi86 初始代码:

int sn65dsi86_init(void)

{

sn65dsi86_write(0x09, 0x00); // SW Reset

sn65dsi86_write(0x0A, 0x09); // DACP/N CLOCK FREQ 460.8MHz

sn65dsi86_write(0x0D, 0x00); // PLL DISABLE

sn65dsi86_write(0x10, 0x26); // Single channel DSI receiver A, DSIA 4Lanes

sn65dsi86_write(0x11, 0x00); // CHA/B DSI DATA/CLK EQ

sn65dsi86_write(0x12, 0x59); // DSIA CLK FREQ 445~450MHz

sn65dsi86_write(0x5A, 0x05); // enhanced framing and ASSR

sn65dsi86_write(0x93, 0x20); // 2 DP lanes no SSC

sn65dsi86_write(0x94, 0x80); // HBR (2.7Gbps)

sn65dsi86_write(0x5C, 0x01); // HPD DISABLE

sn65dsi86_write(0x0D, 0x01); // PLL ENABLE

mdelay(15);

sn65dsi86_write(0x95, 0x00);

/* Write DPCD Register 0x0010A in Sink to Enable ASSR */

sn65dsi86_write(0x64, 0x01);

sn65dsi86_write(0x74, 0x00, 0x01, 0x0A); // AUX_ADDR: 0x00010A

sn65dsi86_write(0x77, 0x01); // AUX_LENGTH: 1

sn65dsi86_write(0x78, 0x81); // AUX_CMD: 0x8(Native Aux Write), SEND:0x1

mdelay(10);

sn65dsi86_write(0x96, 0x0A); // 0x01: Normal TRAIN, 0x0A: Semi-Auto TRAIN

mdelay(20);

/* W = 1920(0x0780) */

sn65dsi86_write(0x20, 0x80, 0x07);

/* H = 1080(0x0438) */

sn65dsi86_write(0x24, 0x38, 0x04);

/* HS = 44(0x002C) */

sn65dsi86_write(0x2C, 0x2C, 0x00);

/* VS = 5 , CHA_VSYNC_POLARITY active low Pulse */

sn65dsi86_write(0x30, 0x05, 0x00);

/* HBP = 148 */

sn65dsi86_write(0x34, 0x94);

/* VBP = 36 */

sn65dsi86_write(0x36, 0x24);

/* HFP = 88 */

sn65dsi86_write(0x38, 0x58);

/* VFP = 4 */

sn65dsi86_write(0x3A, 0x04);

sn65dsi86_write(0x5A, 0x0D); // enhanced framing, ASSR, and Vstream enable

mdelay(10);

return 0;

}Haibin、

感谢您提供这些详细信息。

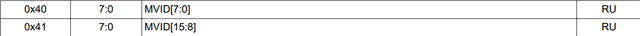

从寄存器日志中、我只能看到这些 DP 寄存器之间的一个区别、MDIV 对于 CSR 不同:

0x40 = 0xCD (205d)-> 0x40 = 0xD2 (210)

这可以从 DisplayPort 的角度看到。

我只能想象、由于 MDIV 值发生变化、这个运行时问题会在时钟延迟或频移后发生、源端或接收端显示是否有任何诊断表明时序发生了变化?

您是否可以尝试将该 MDIV 设置为正常日志值 (0xCD)、并查看屏幕在给定持续时间后是否为空白?

此致、

Miguel

感谢您的回复!

我向屏幕工厂报告了这种现象、他们测量到 eDP 主链路频率为 2.62G、这不符合 VESA 规范。 然后、我调整了 MIPI 时钟(HS/HBP/HFP/VS/VBP/VFP 等)、并将 0x12 寄存器从 0x59 更改为 0x5A。 测得的 eDP 主链路频率为 2.64G、黑屏现象未再次出现、但仍不符合 VESA 规范 2.7G、这可能仍会带来风险。 sn65dsi86 的 0x94 寄存器已确认设置为 2.7G(对应于寄存器值 0x80)。 如何确保 sn65dsi86 的输出主链路频率为 2.7G?

修改后的初始化代码如下所示:

int sn65dsi86_init(void)

{

sn65dsi86_write(0x09, 0x00); // SW Reset

sn65dsi86_write(0x0A, 0x09); // DACP/N CLOCK FREQ 460.8MHz

sn65dsi86_write(0x0D, 0x00); // PLL DISABLE

sn65dsi86_write(0x10, 0x26); // Single channel DSI receiver A, DSIA 4Lanes

sn65dsi86_write(0x11, 0x00); // CHA/B DSI DATA/CLK EQ

sn65dsi86_write(0x12, 0x5A); // DSIA CLK FREQ 450~455MHz

sn65dsi86_write(0x5A, 0x05); // enhanced framing and ASSR

sn65dsi86_write(0x93, 0x20); // 2 DP lanes no SSC

sn65dsi86_write(0x94, 0x80); // HBR (2.7Gbps)

sn65dsi86_write(0x5C, 0x01); // HPD DISABLE

/* W = 1920(0x0780) */

sn65dsi86_write(0x20, 0x80, 0x07);

/* H = 1080(0x0438) */

sn65dsi86_write(0x24, 0x38, 0x04);

/* HS = 44(0x002C) */

sn65dsi86_write(0x2C, 0x2C, 0x00);

/* VS = 8 , CHA_VSYNC_POLARITY active low Pulse */

sn65dsi86_write(0x30, 0x08, 0x00);

/* HBP = 148 */

sn65dsi86_write(0x34, 0x94);

/* VBP = 27 */

sn65dsi86_write(0x36, 0x1b);

/* HFP = 88 */

sn65dsi86_write(0x38, 0x58);

/* VFP = 20 */

sn65dsi86_write(0x3A, 0x14);

sn65dsi86_write(0x0D, 0x01); // PLL ENABLE

sunxi_lcd_delay_ms(20);

sn65dsi86_write(0x95, 0x00);

/* Write DPCD Register 0x0010A in Sink to Enable ASSR */

sn65dsi86_write(0x64, 0x01);

sn65dsi86_write(0x74, 0x00, 0x01, 0x0A); // AUX_ADDR: 0x00010A

sn65dsi86_write(0x77, 0x01); // AUX_LENGTH: 1

sn65dsi86_write(0x78, 0x81); // AUX_CMD: 0x8(Native Aux Write), SEND:0x1

sunxi_lcd_delay_ms(40);

sn65dsi86_write(0x96, 0x0A); // 0x01: Normal TRAIN, 0x0A: Semi-Auto TRAIN

sunxi_lcd_delay_ms(20);

sn65dsi86_write(0x5A, 0x0D); // enhanced framing, ASSR, and Vstream enable

return 0;

}Haibin、

测得 eDP 主链路频率为 2.62G、这不符合 VESA 规范。

这是一个很好的发现。 我同意速率不匹配仍可能构成风险、因此让我们来看看所做的配置更改;

、将 0x12 寄存器从 0x59 更改为 0x5A

这会将传入 DSI 时钟频率的估算范围从 445 –450MHz 更改为 450 –455MHz、但寄存器 0x0A = 0x09 指示时钟应设置为 460.8MHz

也许将传入 DSI 时钟频率设置为 0x5C (460 –465MHz) 将进一步提高此输出数据速率。 匹配较近的速率可让屏幕根据传入的时钟通过恢复是有意义的。

如何确保 sn65dsi86 的输出主链接频率为 2.7G?

我没有看到诊断寄存器在内部捕获 DP 数据速率、但 DP_DATARATE 配置为 2.7Gbps(HBR 模式)、一个选项是测量波形并确保 DP 布线上的眼图、以确保其符合 eDP 1.4 规格。

如果您有任何其他问题、敬请告知。

此致、

Miguel