工具/软件:

尊敬的团队:

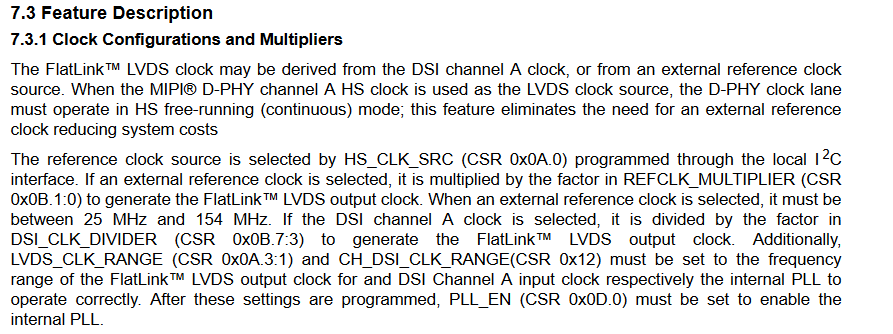

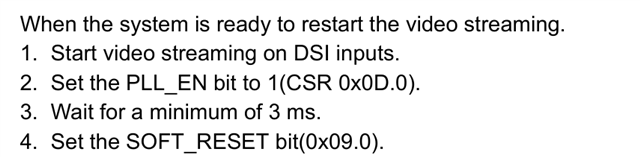

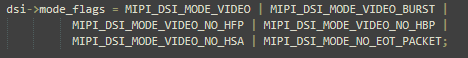

我们目前正在我们基于 QCS615 的平台上启动 TI SN65DSI84 DSI 转 LVDS 桥接器、并运行 Linux 内核版本 6.6。

在验证过程中、我们在 SN65DSI84 驱动器中启用了测试图形生成功能。 但是、LVDS 面板上显示的测试图形不清楚且失真(请参阅所附图像以供参考)。

e2e.ti.com/.../0181.G133HAN01V1-final-spec-ver-1.0_5F00_20190513.pdf.pdfe2e.ti.com/.../panel_5F00_timing_5F00_settings.txte2e.ti.com/.../qcs615_2D00_smarc_2D00_lvds.txt

其他意见:

测试图形被禁用时、LVDS 面板仅显示背光、不显示图像或信号。

我们的硬件配置如下:

LVDS A 承载奇数像素

LVDS B 传输偶数像素

为了供您参考、我们随函附上:

相关器件树片段。 (qcs615-smarc-LVDs.dts)

面板设置 (panel_timing_settings.txt)

面板数据表 (G133HAN01V1 最终规格版本 1.0_20190513.pdf.pdf)

感谢您提供指导来解决此问题并通过 SN65DSI84 桥确保正确的图像显示。

此致、

Sudarshan