工具/软件:

尊敬的 TI 团队:

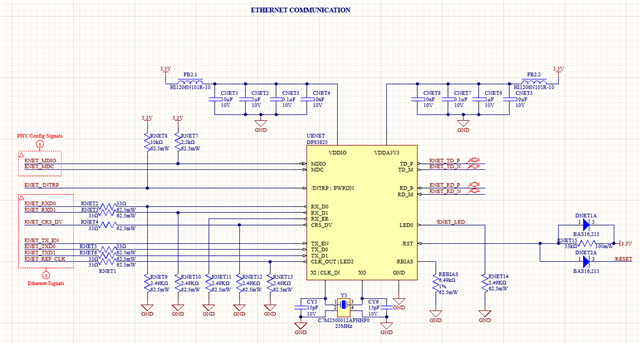

我们将 STM32H757 微控制器与 DP83825I phy(通过 RMII 接口链接在一起)搭配使用、其中该 phy 链接到 25MHz 石英、以便能够为 CPU 提供 50MHz 基准时钟。 当以太网电缆插入 RJ45 连接器(具有集成磁性元件的 RJ45)时、会发生一些通信损耗。 我们使用 phy 给出的参考时钟检查了 MDIO + MDC 信号和 RX0-1/TX0-1 信号、一切似乎都正常(与连接到 NXP 的 LPC54606 微控制器的其他电路相比、该 PHY 链接到该微控制器并正常工作)。

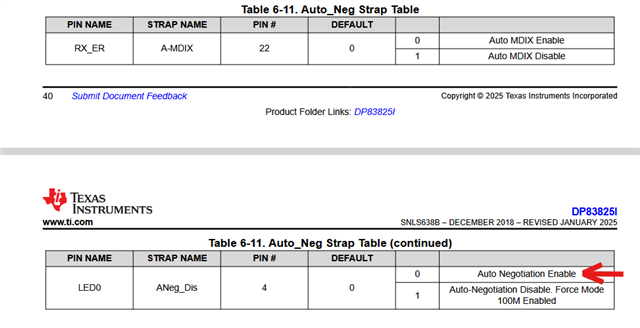

但是、在检查寄存器配置时、我们注意到一些未由我们程序配置的寄存器(例如 LEDCR、MLEDCR 和 PHYSTS)没有数据表指定的默认值。 因此、激活的 LED(链接在 phy 的 LED0 物理引脚上)“默认“具有反极性 (LEDCR 寄存器的位 7 默认为 1、而不是 0)。

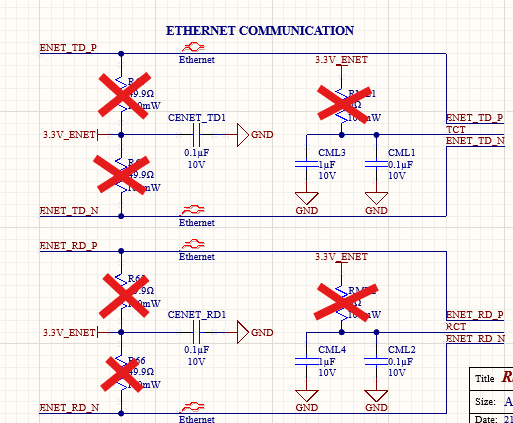

请在附件中找到有关 PHY 接线的原理图:

(没有填充划线的元件)

非常感谢、

此致、

Benjamin