工具/软件:

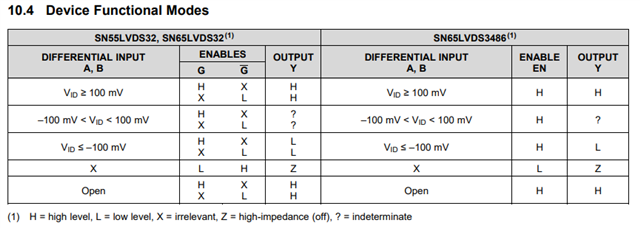

大家好、我正在使用 SN65LVDS32DR 进行设计时遇到的一个问题是、将使能(低电平有效)引脚 G̅ 驱动至高电平 状态不会禁用芯片输出并将它们设置为高阻态。

我的电源电压为 3.3V、我已使用示波器检查 G̅ Ω 引脚 12 上是否存在 3.3V 电压、但输出仍处于活动状态、这导致它们与另一个数字信号驱动器争用。

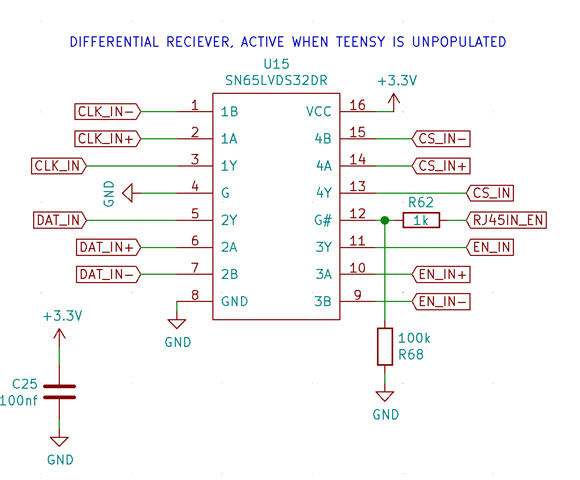

这是我原理图的相关部分:

我使用一个微引脚将 RJ45IN_EN 写入高电平以禁用 SN65LVDS32DR 芯片(因此微控制器可以提供这些信号)、但即使微引脚将 G#(引脚 12)保持在 3.3V、输出仍然与我的微输出争用(显示为压降和噪声)。 在 从电路板上物理移除 SN65LVDS32DR 之前、问题不会消失。

Pleaes 建议这里出现了什么问题、这似乎直接与数据表中所述的行为相矛盾。

谢谢!