工具/软件:

你好。 我正在使用连接到 Xilinx Zynq MPSoC 的 TUSB1210 、.60MHz CLK 由 TUSB1210 生成。

我有 3 个小问题,我很感谢任何帮助。

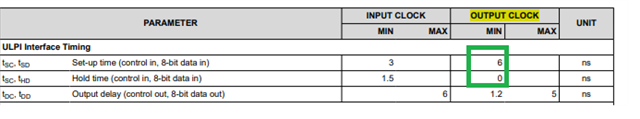

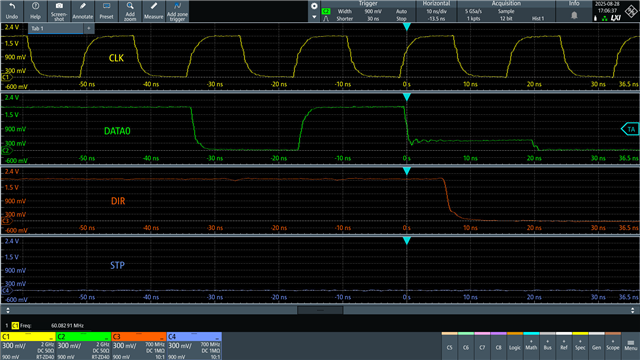

1.我的设置和保持时间测量值是否正确,在下面的屏幕截图,? 我测量到 11.92ns 建立时间和 4.8ns 保持时间。

这是否意味着我可以很好地使用 TUSB1210 时序规格? 建立时间定义为最小 6ns、保持时间定义为最小 0ns。

(请忽略数据边沿上的非单调小凸点,我在布线的错误一侧 (驱动器侧)进行了测量)

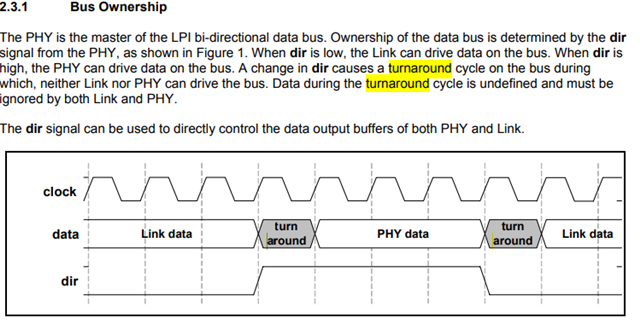

2. DIR =1 时如何测量设置和保持时间?

Xilinx 规格的 建立时间为>4.5ns、保持时间为>0ns。 DIR 变为高电平后、我是否应该忽略第一个 CLK 边沿?

在我的屏幕截图中,一个 jest 之前的 0 点。

3.我注意到,有时在数据线上我看到~0.4V“尾巴“。 它会 在 1 个时钟周期内保持在~0.4V。 它始终 在 DIR 变为低电平时发生。

这是否符合预期? 我应该担心这一点吗? Zynq VIL_MAX 为 0.63V、因此我有一些 裕度、但 TUSB1210 上的 VIL_MAX 为 0.45V。

谢谢您、

Rafal