主题:DP83869 中讨论的其他器件

工具/软件:

它可能与之有关的人:

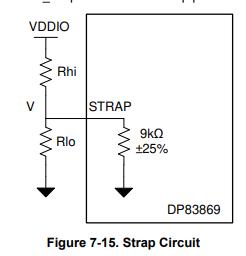

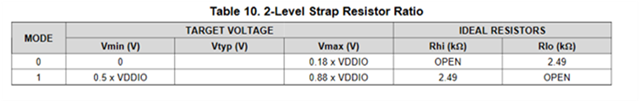

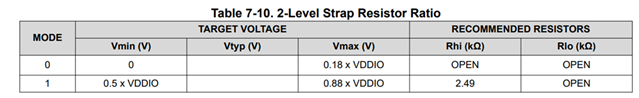

请注意、DP83869 数据表的版本从 C 到 D、更新了“四级配置 (strap) 模式 0 Rlo 建议从 2.49k 更改为开路“。 我假设参考表 10 2 级 Strap 配置电阻比而不是 4 级 Strap 配置、因为模式 0 Rlo 从 2.49k 更改为开路。

修订版 C:

修订版 D:

考虑到这一点、我们遵循了数据表修订版 C (2 级应用的 Rlo = 2.49k)。 几个问题:

-这种自举电阻变化的原因是什么?

-您建议我们不安装 Rlo 以与修订版 D 保持一致吗?

-由于 JTAG_TDO 是一个多用途的引脚,如果我们计划使用 JTAG 边界扫描,我们该如何将它绑定?

谢谢、

Brendan