主题中讨论的其他器件:AM6442、 DP83869、 TMDS64EVM

工具/软件:

我们计划使用 RJMG2330A1610ER (Amphenol)、因为我们的设计中存在空间限制。 它是一个具有集成磁性元件的堆叠式 RJ45 + USB A 连接器、额定值适用于 1000BASE-T 和 AutoMDIX。

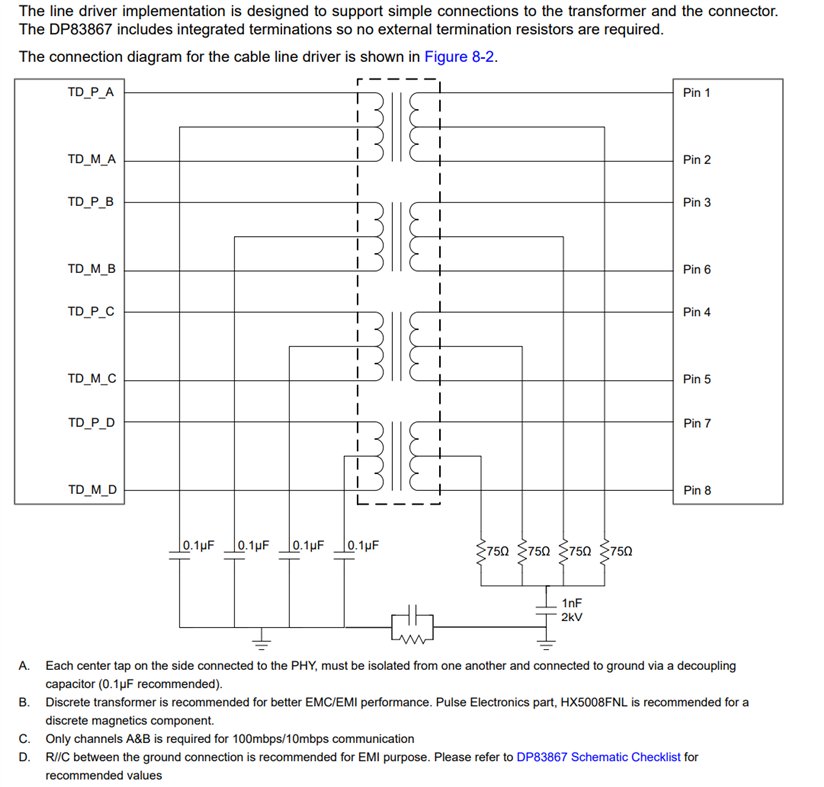

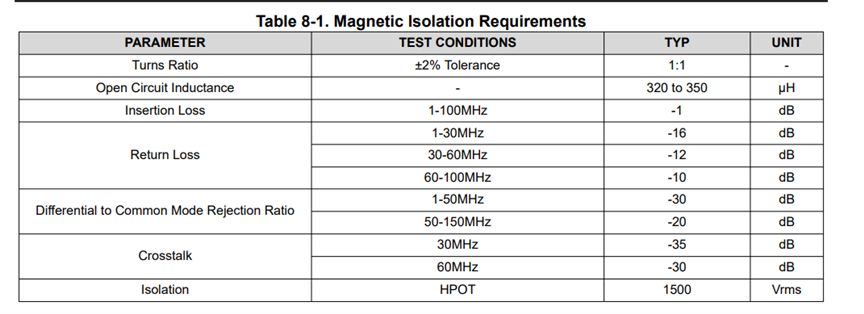

我们的 PHY DP83867IRRGZT 、我们注意到 RJMG2330A1610ER 的内部磁性元件配置与 TI 参考设计中推荐的变压器拓扑不同。

您能否确认此连接器是否与 DP83867IRRGZT 兼容?

具体来说:

- 内部磁性元件是否适用于 PHY 的信号要求?

- 中心抽头偏置和端接网络是否符合 TI 的建议?

- 将此连接器与 DP83867IRRGZT 配合使用时、是否有任何已知问题或设计注意事项?

谢谢、

Pradeepraj M