主题: DP83869 中讨论的其他器件

工具/软件:

您好:

我正在使用 Processor SDK Linux 09.02.00.05 开发 J784S4。在我们的设计中、DP83869HM PHY 用作网桥

- Sgmii 连接到 CPSW MAC (J784S4 SerDes2)、

- RGMII 连接到外部 PHY (ADIN1100)。

我当前的 DTS 配置如下所示

-

&SERDES_wiz2{

状态=“正常“;

};

{&S serdes2}

状态=“正常“;

#address-cells =<1>;

#size-cells =<0>;

serdes2_sgmii_link:PHY@0{

reg =<0>;//通道索引

CDN、num-lanes =<1>;

CDN、phy-type = ;

#phy-cells =<0>;

RESET =<&SERDES_wiz2 1>;

};

};

&main_cpsw0{

状态=“正常“;};

&main_cpsw0_mdio{

状态=“正常“;

pinctrl-names =“default";“;

pinctrl-0 =<&main_cpsw9x1_pins_default>;

pinctrl-1 =<&MAIN_PMX_gpio_vddshv20_pins_default>;main_phy3:Ethernet-phy@3{

reg =<3>;// DP83869 地址

TI、工作模式= ;};

adin1100:Ethernet-phy@0{

REG =<0>;// ADIN1100、在 DP83869 后面

PHY-MODE =“RGMIG";“;

};

};&main_cpsw0_port5{

&SERDES_ln_ctrl{

状态=“正常“;

PHY-MODE =“SGMII";“;

phy-handle =<&main_phy3>;

Phys =<&cpsw0_phy_gmii_sel 5>、<&serdes2_sgmii_link>;

PHY-NAMES =“MAC",“,"SerDes、"SerDes "“ ";“;

};

空闲状态= 、 、

、 、

、 、

、 、

< J784S4_SERDES2_LANE0_QSGMII_LANE5 >、 、 ;

};

在 DP83869 驱动程序 (dp83869.c) 中、DP83869_RGMII_SGMII_BRIDGE选中后、它将写入:

RET = phy_MDIFT_MMD (phydev、DP83869_DEVADDR、DP83869_OP_MODE、

DP83869_SGMII_RGMII_BRIDGE、

DP83869_SGMII_RGMII_BRIDGE);

根据数据表(第 7.6.1.122 节、OP_MODE_DECODE 寄存器):

-

位 6 = 0→SGMII 至 RGMII 桥接器(预期模式)

-

位 6 = 1→RGMII 至 SGMII 桥接器

我的问题是:

-

我的 DTS 配置是否足以出现 SGMII→RGMII 桥接模式 ?

-

对于此桥接模式、是否需要在 DTS 中添加任何额外的属性(如内部延迟,FIFO 深度等)?

-

由于驱动器当前设置位 6 = 1、因此是否需要额外的 DTS 标志或配置才能使其适用于 SGMII→RGMII?

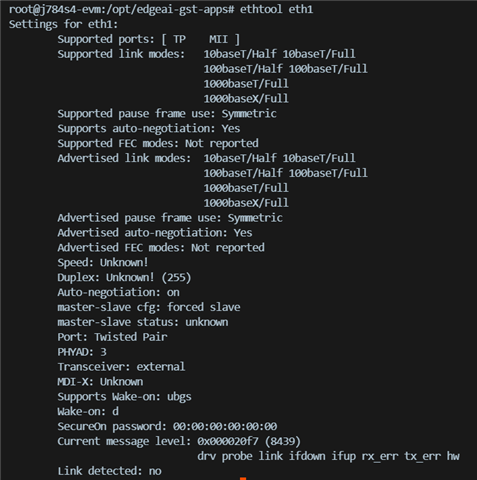

目前是 ADIN1100 侧没有连接链路

谢谢、

Apuroop Kumar。