主题:DP83869 中讨论的其他器件

工具/软件:

大家好!

SoC:Zynq MPSoC (Xilinx /AMD)

MAC 接口:GEM1

PHY 和模式:DP83869 (TI) 和 RGMII 铜缆

中断配置为如下级别触发

&gem1{

PHY 模式=“RGMII-id";“;

状态=“正常“;

phy-handle =<&phy1>;

phy1:PHY@1{

reg =<1>;

兼容=“Ethernet-phy-IEEE802.3-C22";“;

RX-INTERNAL-DELAY-ps =<2000>;

tx-internal-delay-ps =<2000>;

Interrupt-parent =<&GPIO>;

Interrupts =<78 8>;//EMIO 0 用作 INT

};

};

使用“macb ff0c0000.ethernet eth0:PHY [ff0c0000.ethernet-ffffffff:01]驱动程序[TI DP83869](IRQ=52) 配置中断、而 cat /proc/interrupts 中还提供了相应条目。

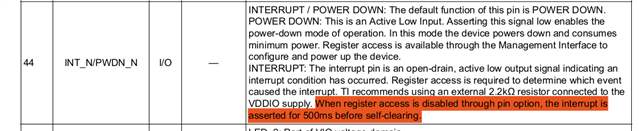

默认情况下、当未连接电缆时、INT 线路会探测到高电平并读为高电平。 当电缆连接链路接通时、cat /proc/interrupt 中的计数器会增加、并且 INT 线路探测到低电平。 但链路建立后、中断线路保持低电平状态、这会导致虚假中断状态、并使中断被禁用、下面的崩溃。

root@zynqmp-iwg36o:~#[ 1040.510999] irq 52:没有人关心(尝试使用“irqpoll"选项“选项引导选项引导)

[1040.517716] CPU:0 PID:0 Comm:swapper/0 未污染 6.6.40-Xilinx gf2d46953498a #1

[ 1040.525463]硬件名称:xlnx、zynqmp (DT)

[1040.529639]呼叫跟踪:

[1040.532077] dump_backtrace+0x90/0xe8

[1040.535749] SHOW_STACK+0x18/0x24

[1040.539073] dump_stack_lvl+0x48/0x60

[1040.542736] dump_stack+0x18/0x24

[1040.546051]__REPORT_BAD_IRQ+0x38/0x120

[1040.549975] note_interrupt+0x310/0x360

[ 1040.553811] Handle_IRQ_event+0xd8/0xe8

[1040.557648] Handle_fastei_irq+0xb0/0x284

[1040.561745] generic_handle_domain_IRQ+0x2C/0x44

[1040.566371] Zynq_GPIO_irqhandler+0xa0/0x16c

[ 1040.570642] generic_handle_domain_IRQ+0x2C/0x44

[1040.575268] GIC_HANDLE_IRQ+0x6C/0x9C

[1040.578931] CALL_ON_IRQ_STACK+0x24/0x4c

[ 1040.582855] Do_interrupt_handler+0x80/0x84

[1040.587038] el1_interrupt+0x34/0x54

[ 1040.590614] el1h_64_IRQ_HANDLER+0x18/0x24

[1040.594711] el1h_64_IRQ+0x64/0x68

[1040.598114] default_idle_call+0x28/0x3c

[1040.602037] DO_IDLE+0xac/0x100

[1040.605180] CPU_STARTUP_ENTRY+0x34/0x3c

[ 1040.609103] kernel_init+0x0/0x1e0

[1040.612505] arch_post_acpi_Subsys_init+0x0/0x8

[1040.617036] start_kernel+0x504/0x60c

[1040.620699]__PRIMARY_SWITCHED+0xbc/0xc4

[1040.624710]处理程序:

[ 1040.626975][<000000008cd40a2e>] IRQ_DEFAULT_PRIMARY_HANDLER 线程[<00000000054f5eA5>] phy_interrupt

[ 1040.636480 ]禁用 IRQ #52

如何确认是否调用了 PHY 中断处理程序并为中断提供服务(通过向右读取 ISR 寄存器)?

如果手动读取 ISR 寄存器或某个时间后在中断处理程序函数中读取 0x0、其读数为 0x0。

请帮助调试中断为何保持低电平而不是取消置位。