Other Parts Discussed in Thread: DP83867CS, AM625

主题中讨论的其他器件: AM625

工具/软件:

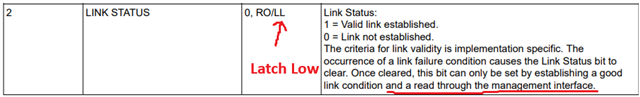

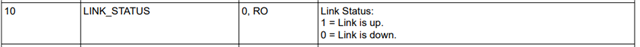

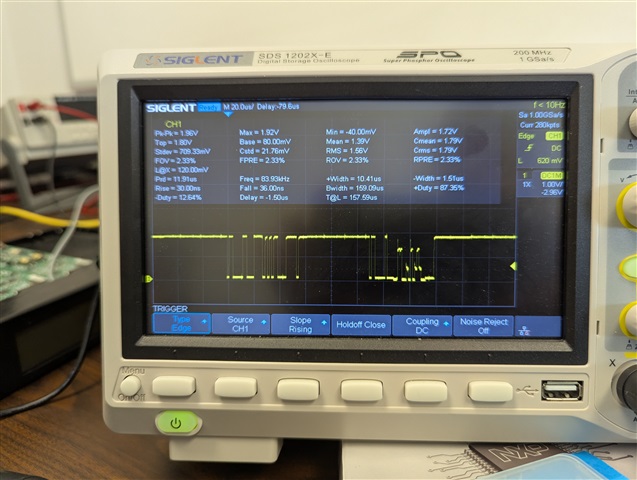

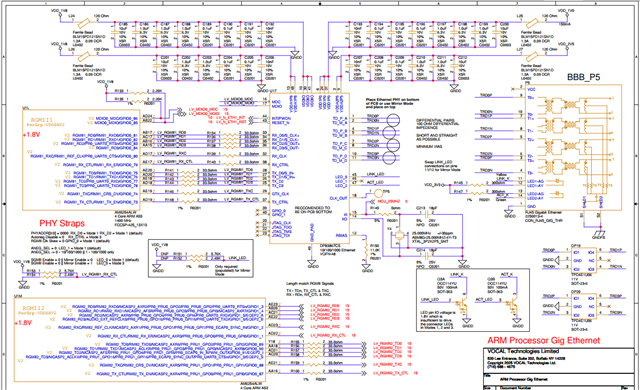

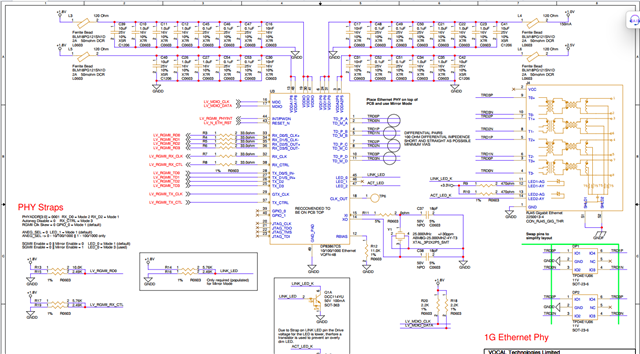

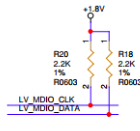

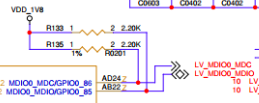

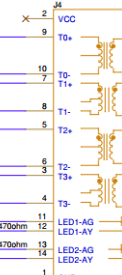

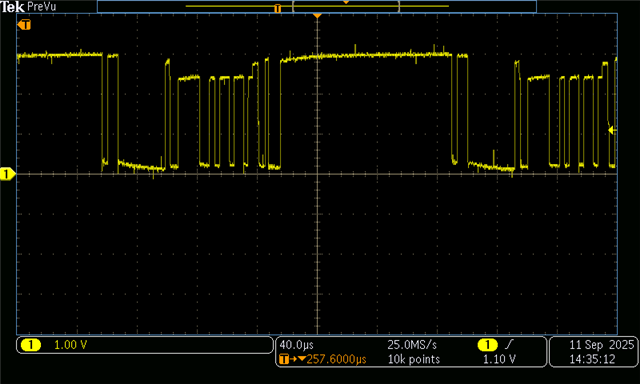

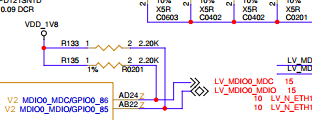

我们发现 DP83867CS 的链路状态未通过 MDIO 可靠读取。 我们的新电路板 Beagle Violet 使用运行 Linux 的 AM625 主机处理器。 默认情况下、MDIO 使用 bit-banging(不是硬件)。 这一选择可能是因为在使用不同(非 TI)PHY 的 BeaglePlay 上早期实现了 AM625。 是否有任何理由将位分组 MDIO 与此 TI PHY 一起使用? 是否有任何关于链路状态不可靠的经验?

我们通过在链路看起来从向上到向下时两次读取 PHY 状态来避免此问题。 这大大提高了我们的可靠性(但它是我们希望避免的 Linux 驱动程序的改变)。 我们还注意到、第二个以太网端口上的读数错误、未连接。