工具/软件:

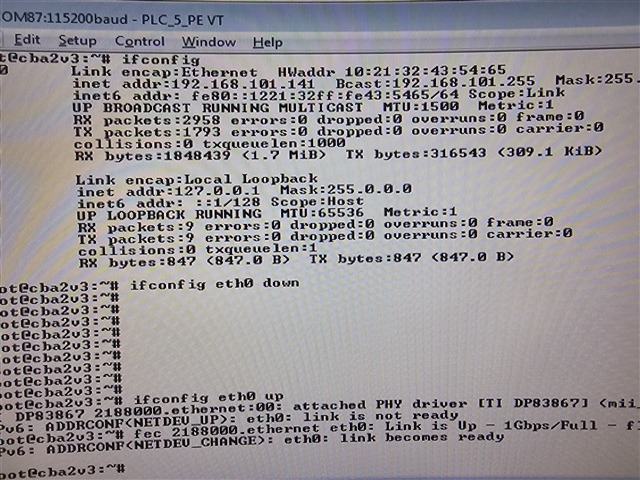

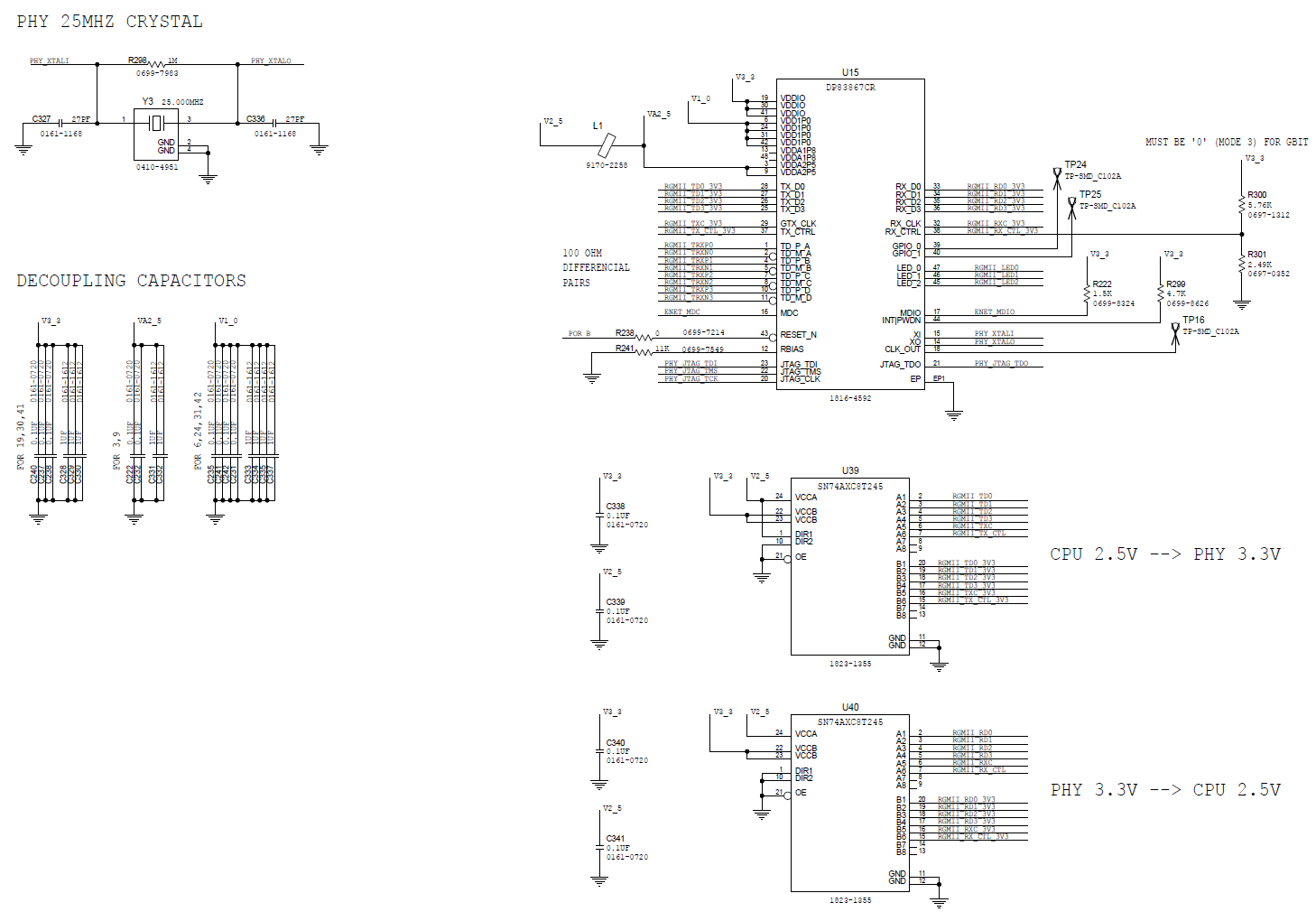

我修改了 A 正常工作 我用替换了 Marvel 88E1118R PHY 的设计 TI DP83867CRRGZ 物理层。

PYH 位于带有 i.MX6 四核 CPU 的 daughtboard 上、 主板上有 RJ45 连接器 (MagJack V890-1AX1-A1)。

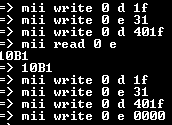

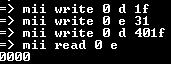

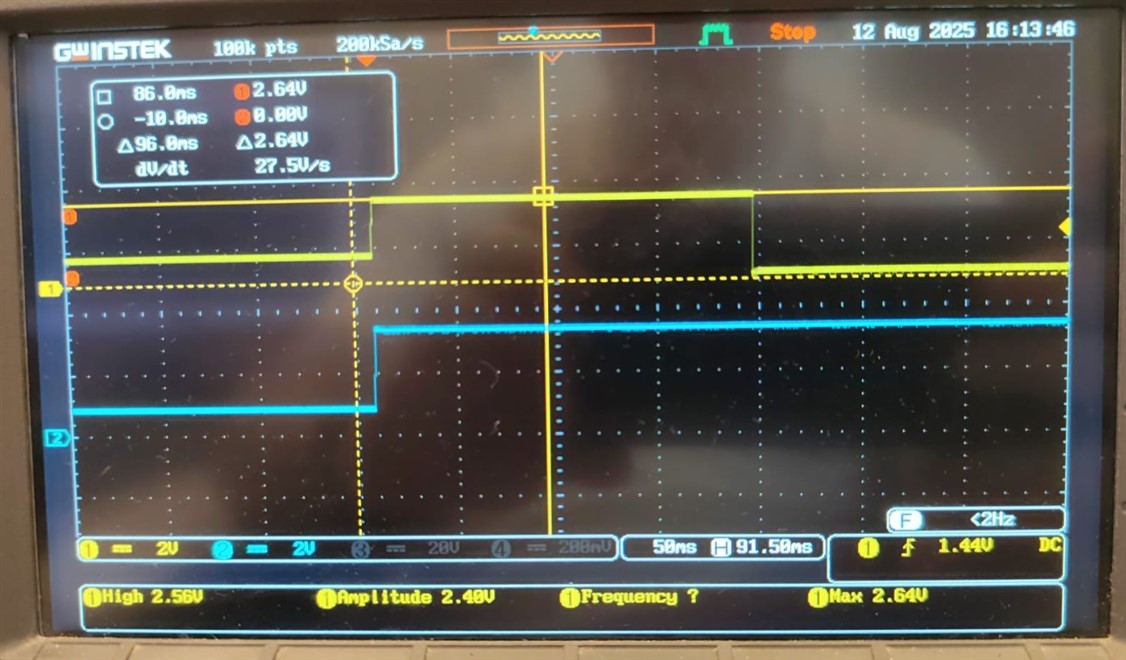

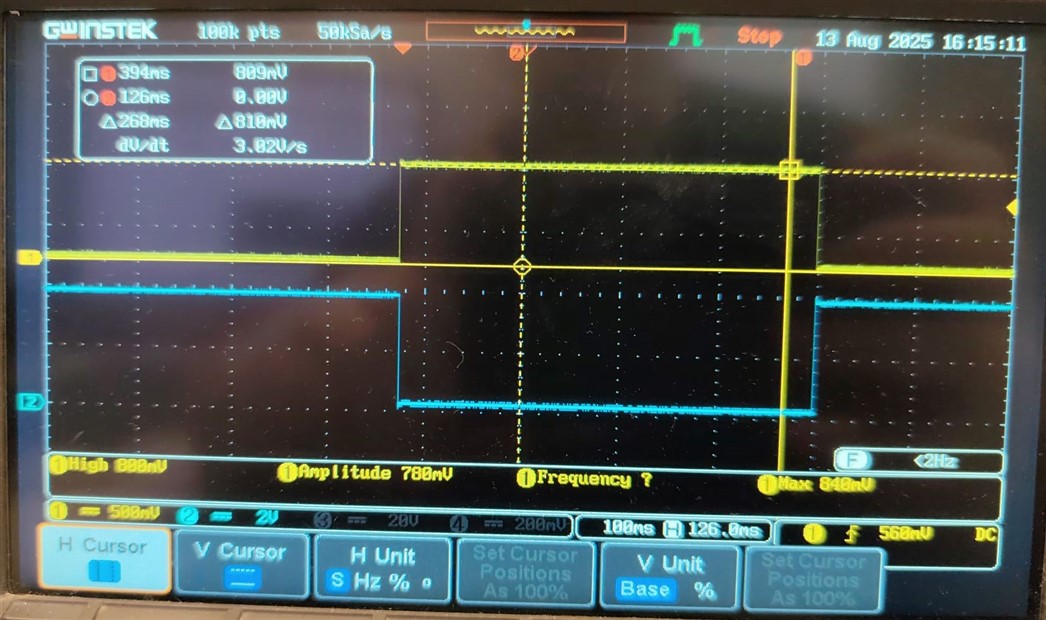

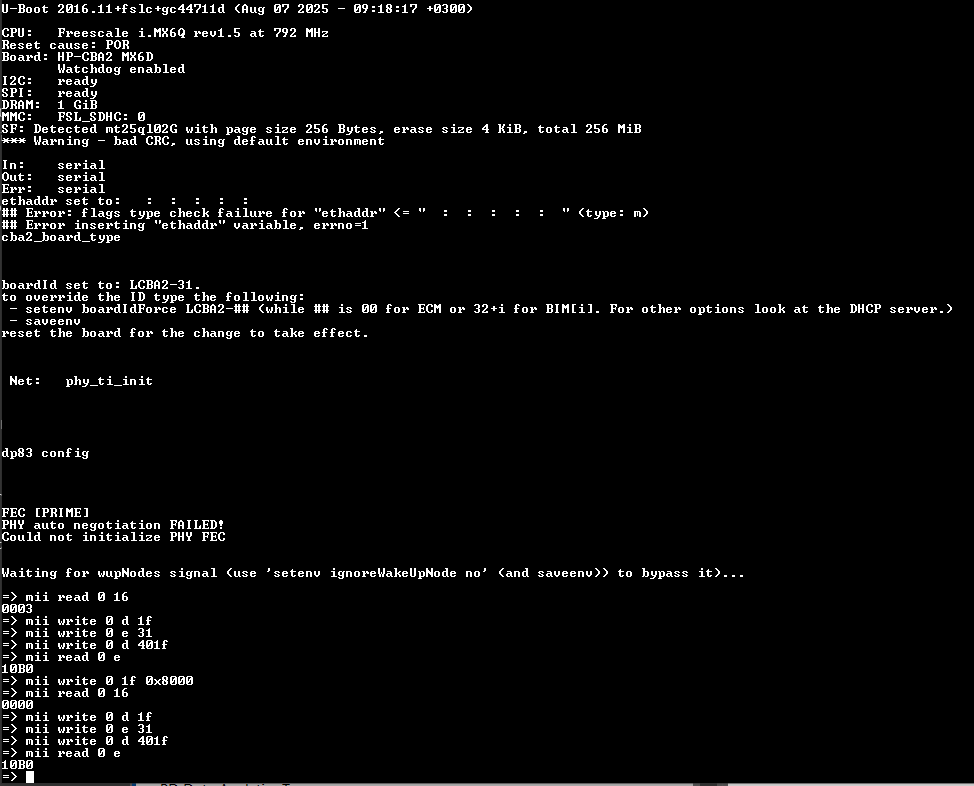

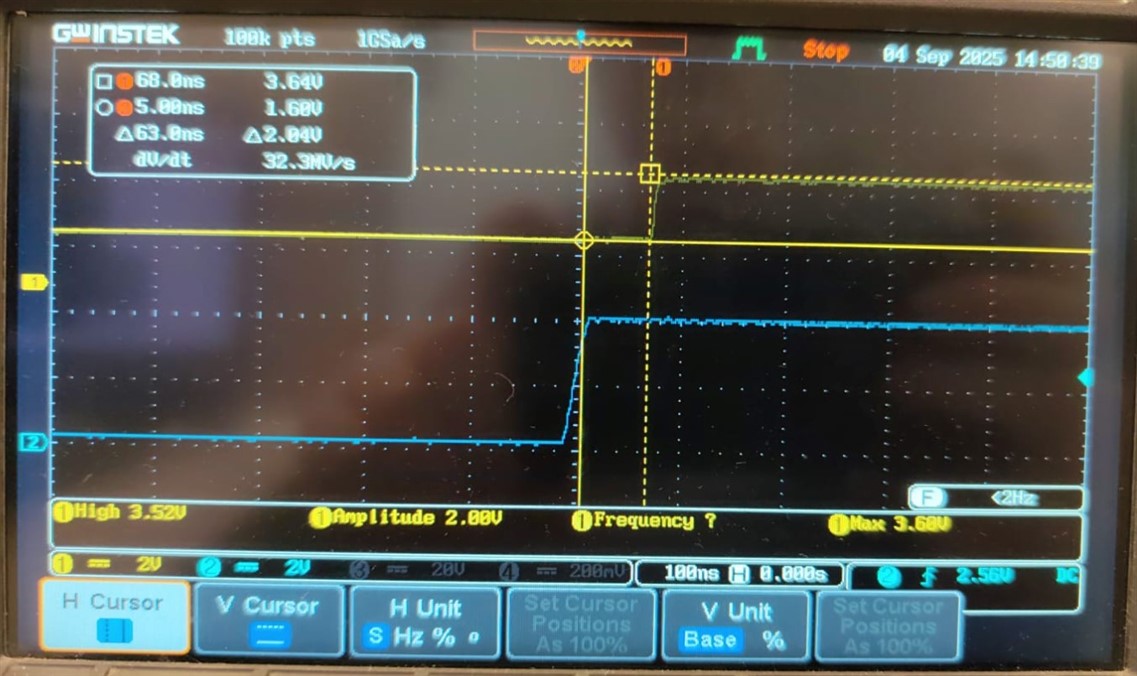

MDIO/MDC 接口正在工作 很好 在 250kHz 下(使用示波器测量)、寄存器如下:

=> MII 读取 0 0

114

=> MII 读取 0 1

794d.

=> MII 读取 0 2.

2000

=> MII 读取 0 3.

A231

=> MII 读取 0 4.

01E1

=> MII 读取 0 5.

0000

=> MII 读取 0 6.

0064

=> MII 读取 0 7

2001.

=> MII 读取 0 8

0000

=> MII 读取 0 9

0300

=> MII 读取 0A

4000

=> MII 读取 0 b

0000

=> MII 读取 0 c

0000

=> MII 读取 0 d

0000

=> MII 读取 0 e

0000

=> MII 读取 0 f

3000

=> MII 读取 0 10

1012

=> MII 读取 0 11

0402.

=> MII 读取 0 12

0000

=> MII 读取 0 13

0400

=> MII 读取 0 14

29C7

=> MII 读取 0 15

0000

=> MII 读取 0 16

0003.

=> MII 读取 0 17

0040

=> MII 读取 0 18

6150

=> MII 读取 0 19

4000

=> MII 读取 0 1a

0002.

=> MII 读取 0 1b

0000

=> MII 读取 0 1c

0000

=> MII 读取 0 1d

0000

=> MII 读取 0 1e

0002.

=> MII 读取 0 1f

0000

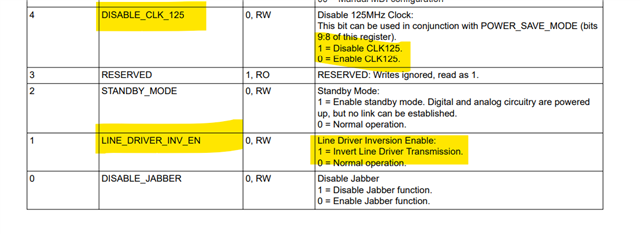

当我启用(“0")“)DISABLE_CLK_125 位(地址 0x10 位 4)时、我会获得良好的时钟信号、这是否与寄存器 0x0170 上的 CLK_O_DISABLE 位相同?

通过更改寄存器 0x0170、可以得到 25MHz(对于默认基准时钟)、125MHz(用于发送和接收通道)和 25MHz(对于接收通道,除以 5)。

CLK_OUT 引脚上的接收和发送时钟是否源自 MAC 接口的 RX_CLK 和 TX_CLK? 还是内部生成的?

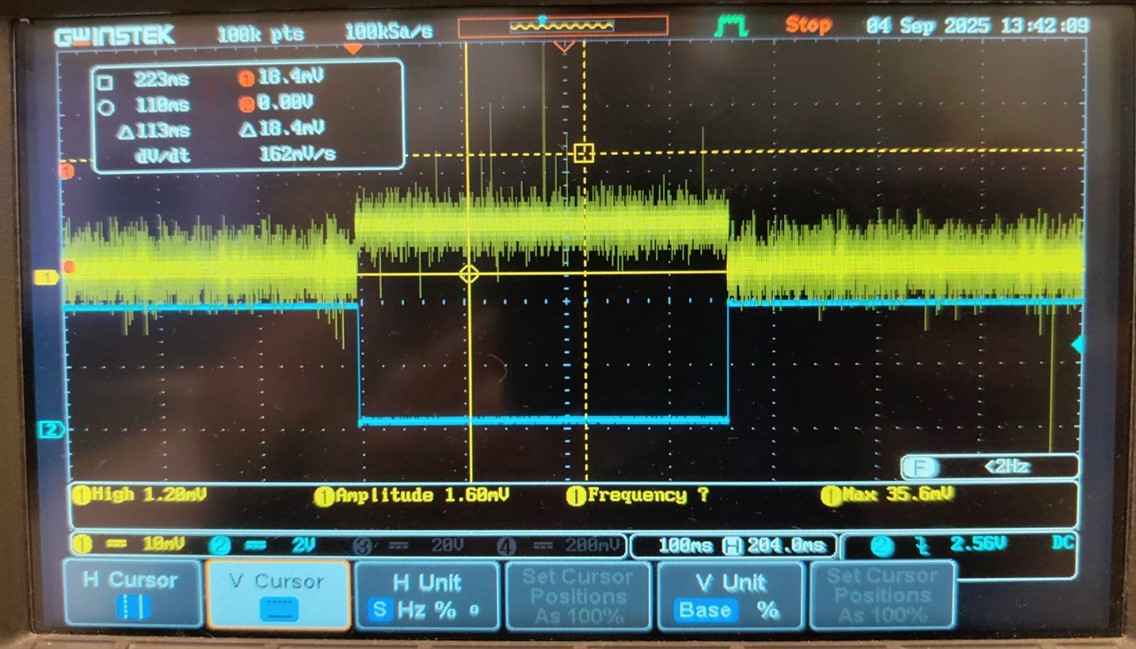

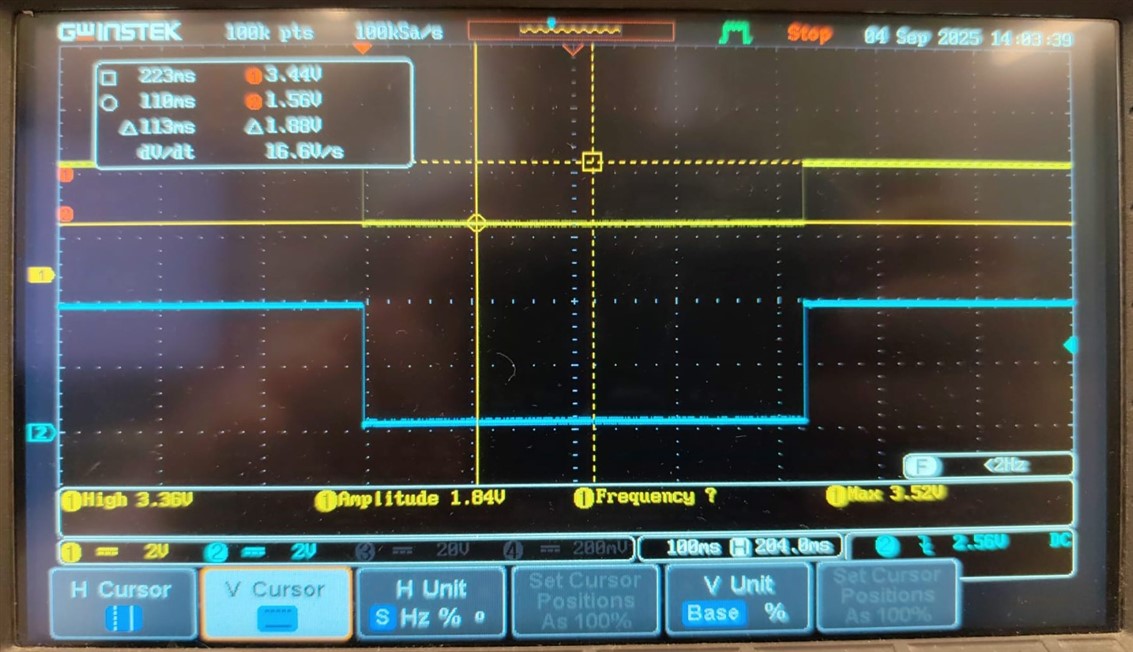

是什么原因导致在未连接电缆的情况下连接链路?

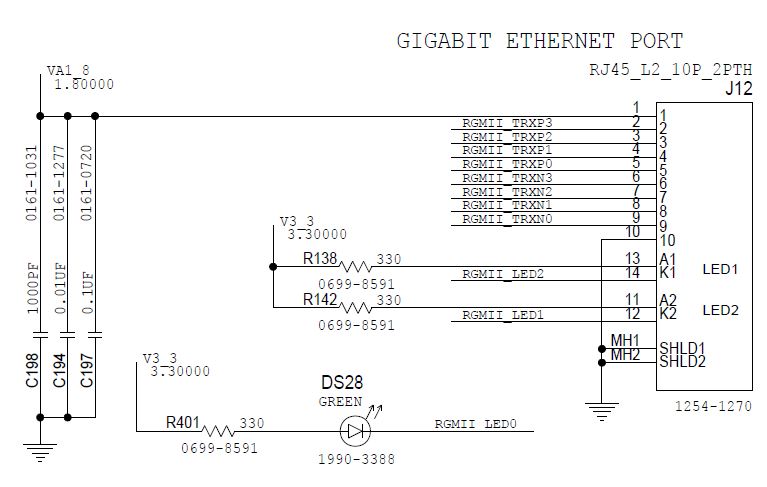

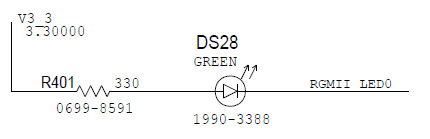

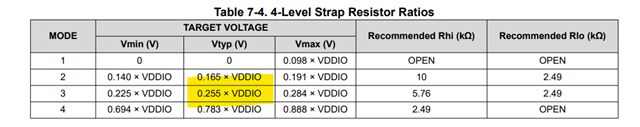

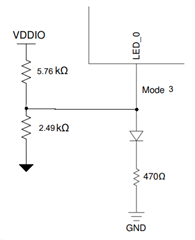

子板原理图

主板原理图 -忽略 1.8V 的抽头它是悬空的(未安装的电阻器在另一页)它是需要 Marvell PHY。