工具/软件:

您好、

我使用 DS320PR1601 来进行新工程。

我将堆叠连接到我们的电路板。

我获得了 TI 的 DS320PR1601 EVM 板详细信息。

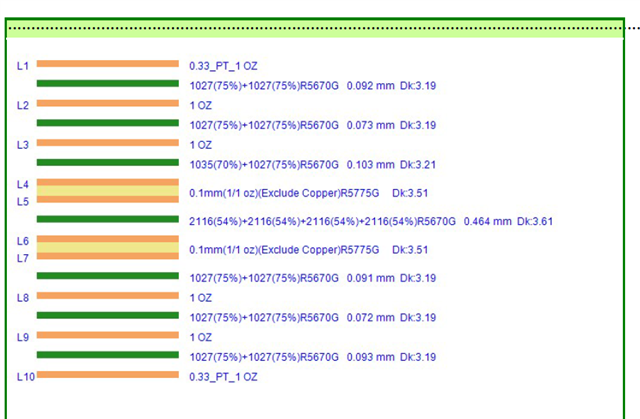

我们还参考了它的布局和堆叠文件。

我们知道在叠层中遵循对称性、而在我们的叠层中、我们无法遵循对称性。

在堆叠时是否需要保持对称?

同样、根据电流堆叠、为了达到 85 Ω 阻抗、布线宽度和间距应大于 7mil。

但我们在顶部只能实现 84.758 Ω、而在底部可以实现 85.423 Ω。

在布线宽度为 7mil 时、我们需要在转接驱动器 IC 附近具有 2mil 的布线宽度差。(即 IC 引脚附近为 5mil)、这样可以吗?

请提供您宝贵的建议。

谢谢。此致、

Shekha Shoukath