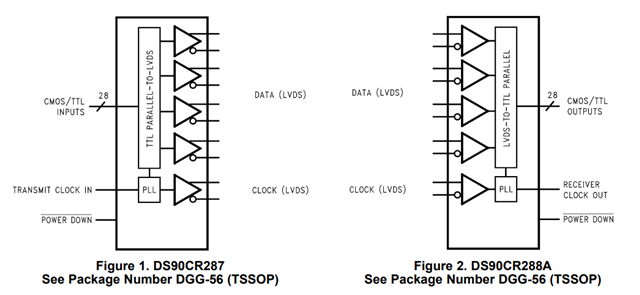

主题中讨论的其他器件:DS90CR288A、

工具/软件:

大家好:

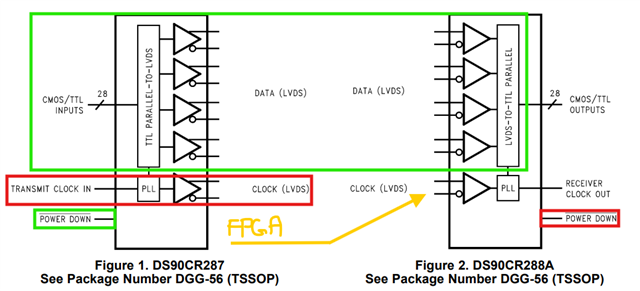

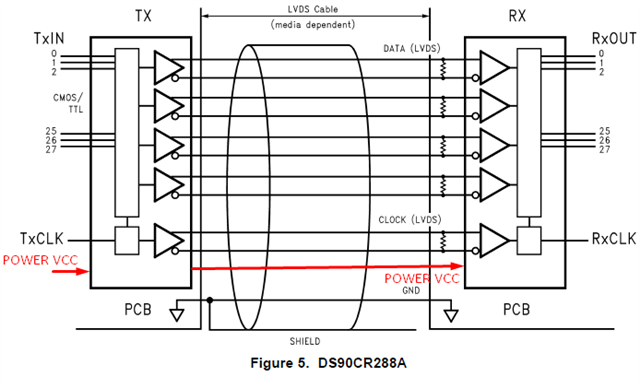

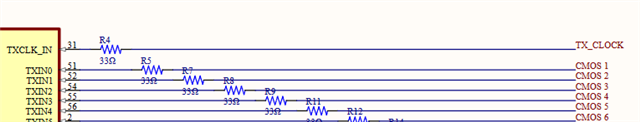

我有 用于 TX 的 DS90CR287 和 用于 RX 芯片的 DS90CR288A。 我在这些芯片之前进行了测试(首次上电)、得到的时钟和数据噪声很小。 设计中使用去耦电容器。 第二次上电我无法从 TX 侧获得任何时钟。 我将带有 FPGA 的差分时钟提供给 RX 芯片、这是有效的。 问题出在 TX 端。 我的启动顺序如下:

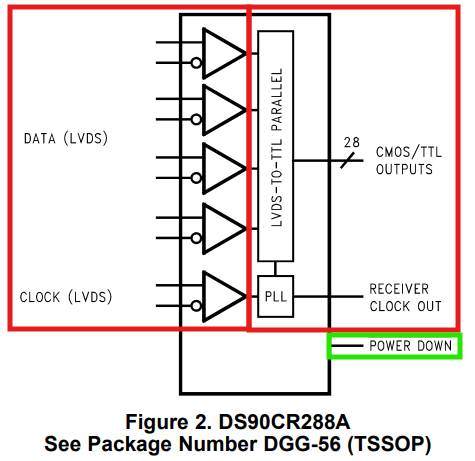

- TX 上电(PWRDWN 为低电平)

- FPGA 上电并同时提供时钟。

- TX PWRDWN 为高电平。

所以参考指南和其他线程我读了什么,告诉我这个 sequeuence。 但我无法获得任何时钟的第二上电部分。 是关于芯片还是 PLL? 所有电压均为 3.3 且接地。 (PLL、LVDS 和 VCC 外部) 我更改了 IC 3 次、得到的结果相同。

感谢您的答复。

此致、