Other Parts Discussed in Thread: DP83867IR

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DP83867IR我有一个配备了 DP83867IR PHY 作为我的 Zynq FPGA 的以太网外设的定制电路板。

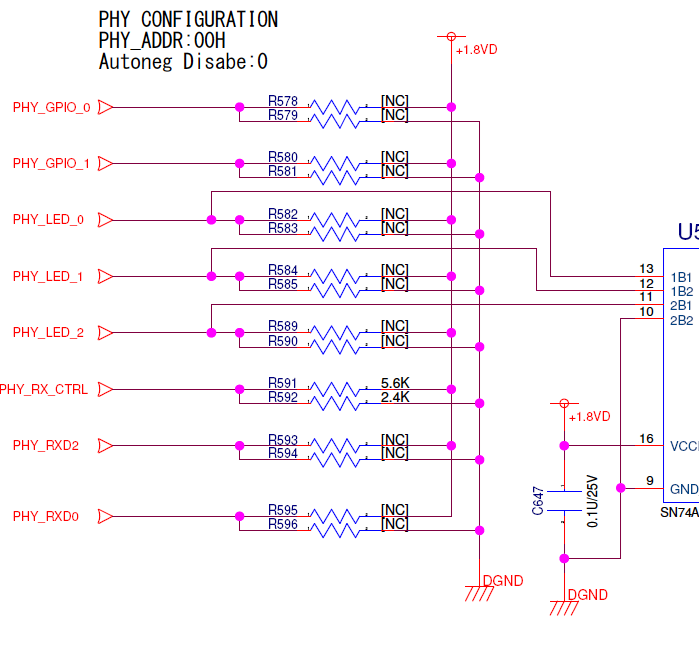

如所示的电路图所示、我将使用 RXD[0]、RXD[2]和 RX_CTRL 端口配置一个 strap。

Zynq FPGA 在复位时进入上拉状态、

上拉电阻值约为 8k【Ω】至 53k【Ω】。

考虑到 Zynq FPGA 的上拉电阻值(约为 8k【欧姆】至 53k【欧姆】)、R596、R594、R591 和 R592 应该是什么电阻值?

提前感谢您。