主题中讨论的其他器件: DP83869、 DP83869EVM

工具/软件:

我在使用连接到 TI DP83869HM PHY 的 Xilinx Versal Premium GEM 0 MAC 时遇到两个问题。

问题 1: 无法从 Linux 笔记本电脑 ping 通以太网接口。

问题 2:PHY 环回模式似乎无法在 100Mbps 或 1Gbps 速度下工作。

随附原理图模型。 PHY 通过板对板连接器连接到磁性元件和 RJ45 连接器。 MAC PHY 接口为 RGMII。

e2e.ti.com/.../ti_5F00_dp83869hm_5F00_schematic.pdf

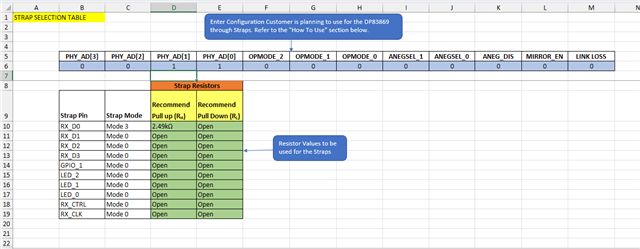

Excel 3324.DP83869_PHY.xlsx 工作表中的 Schematic_Design_Review_Checklist Strap 配置设置:

MDIO 接口可以正常工作、我能够从器件转储 PHY 寄存器。 该寄存器转储还显示了 GEM0 MAC 设置。

e2e.ti.com/.../Ethernet_5F00_mac_5F00_phy_5F00_default_5F00_values.txt

Linux 测试笔记本电脑和嵌入式平台之间有一个到交换机的连接。 链路状态确实反映了嵌入式平台的当前设置 (100Mb/s 或 1Gb/s,具体取决于我们尝试测试的模式 — 表示自动协商似乎正常工作)。 注意:为 PHY 执行外部环回测试时、我们从开关断开连接、并使用 PHY 数据表中所示的环回软件狗。

问题 1

- ping 会强制显示 ARP 消息(通过 Wireshark 观察)、询问谁具有 IP 地址、Versal 代码永远不会接收到进行处理的 ARP 请求(通过调试器观察到)。

- Xilinx 的代码(emacps 驱动程序)可与其开发套件上的不同 PHY 配合使用。

问题 2

- 我们尝试了 100Mb/秒和 1000Mb/秒

- RGMII 根据速度正确更改时钟((25MHz 时钟在 100Mb/s 模式下运行、<xmt-block1>125MHz</xmt-block> 时钟在 1000Mb/s 模式下运行)</s>125MHz

- 在示波器上观察时、RGMII 信号看起来相对干净(未捕获任何信号,但在需要时可能捕获)。

- 环回测试限制为 100Mb/s 模式、以便在切换到 1000Mb/s 之前首先使其正常工作

- 100Mb/s 在 MII 环回中没有要求像 PHY 中的 1000Mb/s 引擎那样设置下游环回模式的要求。

- 中断线路未连接、但 PHY 状态和中断状态显示在 PHY 中接收到页。

- 但是、问题是在任何环回模式下都没有任何东西发送回 MAC(跳过模拟环回模式,因为我们连接到磁性元件,无法满足终端器要求)

- 最初的 PHY 地址为 0、但无法使 PHY 响应 MDIO 命令、因此更改为地址 3 Strap 配置。

- MAC 内部环回按照设计运行(但 PHY 不在其环路中)。

- 将 UDP 用于无连接协议。 已尝试使用相同的 SRC/DST IP 地址、不同的 SRC/DST 地址和广播模式。

- 已注意到、同一 SRC/DST 地址测试可能在 Xilinx 代码中短路、并且从不会碰到硬件。

感谢您的帮助!