器件型号: SN65DP159

大家好、支持团队。

我的客户目前正在进行 HDMI 1.4 合规性测试、有些测试项目显示失败。 您能帮助我解决这个问题吗?

附件为结果报告。

■ID7-2.

更改寄存器设置中的以下各项是否应该改善?

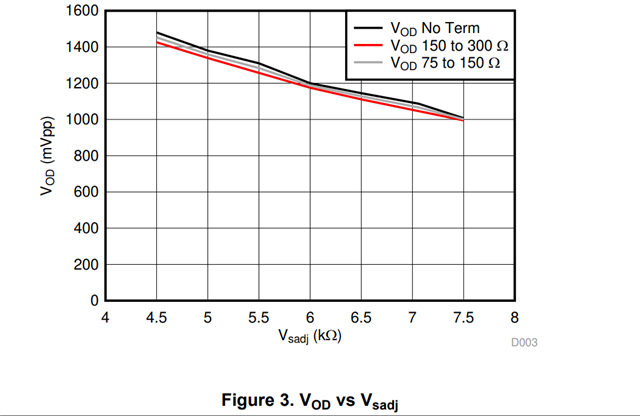

VSWING_DATA:数据输出摆幅控制

VSWING_CLK:时钟输出摆幅控制

■HF1-4

尽管此时未找到有效的对策、但连接器设备之间的布线长度如下:

您能否就导致问题的原因提出建议?

D0_P 7.085280mm -

D0_N 7.085300mm –0.000020

D1_P 7.085280mm -

D1_N 7.085300mm –0.000020

D2_P 7.085280mm -

D2_N 7.085300mm –0.000020

CLK_P 7.085280mm -

CLK_N 7.085300mm –0.000020

此致、

HIG