Other Parts Discussed in Thread: TS3DV642

部件号: TS3DV642

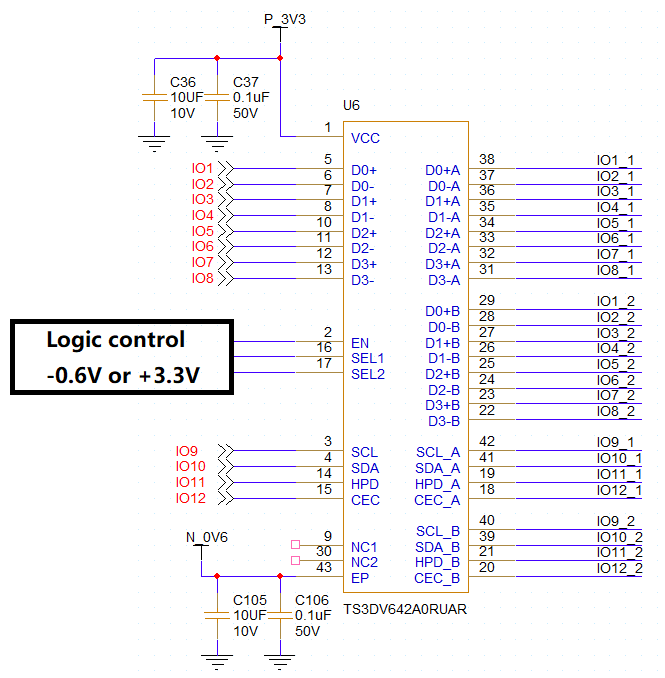

如果 I SUPPLY 向 TS3DV642 的 GND 引脚提供–0.6V 电压、向 VCC 提供 3.3V 电压、同时将 EN/SEL1/SEL2 的逻辑低电平保持在–0.6V、并将逻辑高电平保持在 3.3V 电压、TS3DV642 内的模拟开关是否仍能正常工作? 在这些条件下、器件性能是否会显著下降?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

这些信号用于开路/短路测试选择开关。 在开路/短路测试模式下、IO1_1 至 IO12_1 上的电压范围为–0.4V 至 1.8V。 但是、TS3DV642 的内部二极管会将 IO1_1 钳位到 IO12_1、电压约为–0.4V。 只有在 TS3DV642 的 GND 上施加负电压、才能确保开路/短路测试功能不受干扰。 我的理解是、该芯片的内部电路是 MOS 导通电路。 只要 MOS 导通、就可以保证开关功能。 向 GND 施加负电压不应影响器件的功能。 请帮助确认这一点。 谢谢你。

尊敬的 Zhongfei:

感谢您的澄清。 您认为 TS3DV642 使用基于 MOSFET 的模拟开关是正确的、这些晶体管从根本上关心相对电压关系 (VGS 和 VDS)。 通过将接地基准转换为–0.6V、同时将 VCC 保持在 3.3V、可产生 3.9V 的有效电源电压、这样 MOSFET 开关在启用后应该能够正确导通。 3.9V 有效电源电压提供低于 rec 最大值 4.5V 的足够裕度。 只要您的微控制器或逻辑驱动器能够输出适当的电平:–0.6V(用于逻辑低电平)和+3.3V(用于逻辑高电平)、控制逻辑就应正常运行。 总的来说、我认为在这些条件下器件性能不应该显著下降。 (Ron 可能显示稍高的值)

谢谢您、

Arya