Other Parts Discussed in Thread: SN65DSI83

器件型号: SN65DSI83

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Haiei:

对于 EN 引脚、请检查数据表初始化序列以及 EN 引脚控制。 它描述了应何时设置 EN 引脚。

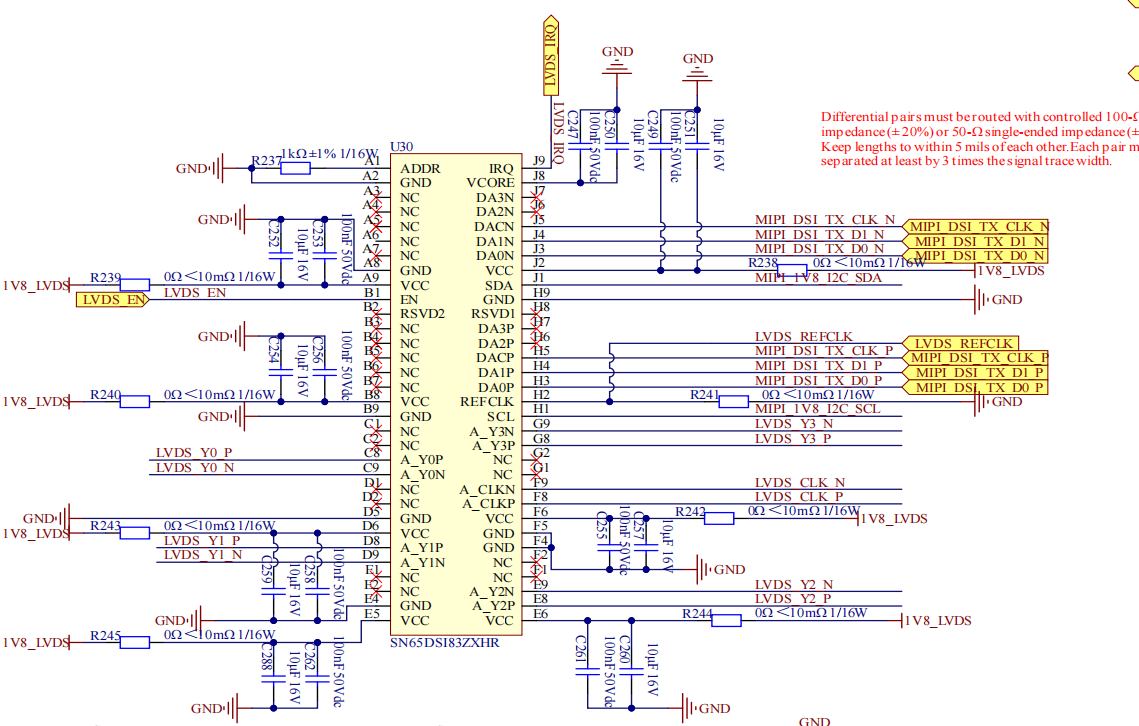

如需使用 REFCLK、DSI 调谐器 GUI 中有一个选项、可将时钟源从 DSI 时钟更改为 REFCLK。 您可以设置倍频器、使 LVDS 时钟输出是 REFCLK 的倍数。

例如、如果 REFRCLK = 24MHz、且倍频器设置为 2、则生成的输出 LVDS 时钟将 为 48MHz。

此致、

Ikram

尊敬的 Haiei:

是的、这应该没问题。 LVDS 输出将为 3 通道或 4 通道、具体取决于每像素位数(色深)。 使用的 DSI 通道数存在差异、输入也会有所不同。

但请注意、必须根据使用的 DSI 通道数以及针对该分辨率产生的 DSI 时钟速率对器件进行编程。

如果您有其他问题、或对 使用 DSI 调谐器工具有任何疑问、敬请告知。

此致、

Ikram

尊敬的 Haiei:

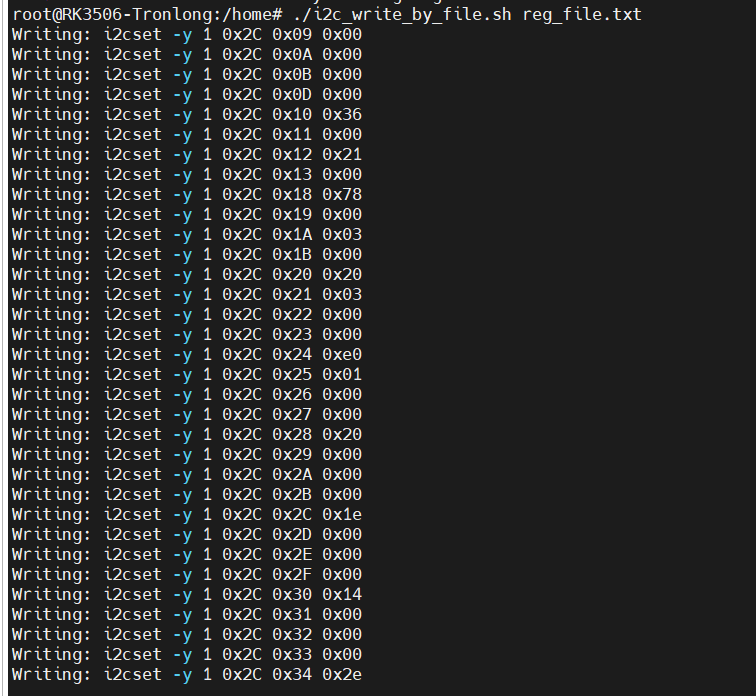

数据表似乎不一致。 该工具需要将 0x36 写入寄存器 0x10、但数据表中未描述位 1 和位 2。

这些位仅用于通道 B、此处不适用、因此在这里被忽略。 这应该没问题。

您是否尝试过使用测试模式? 请在启用测试图形的情况下进行编程、并检查时序是否正常。

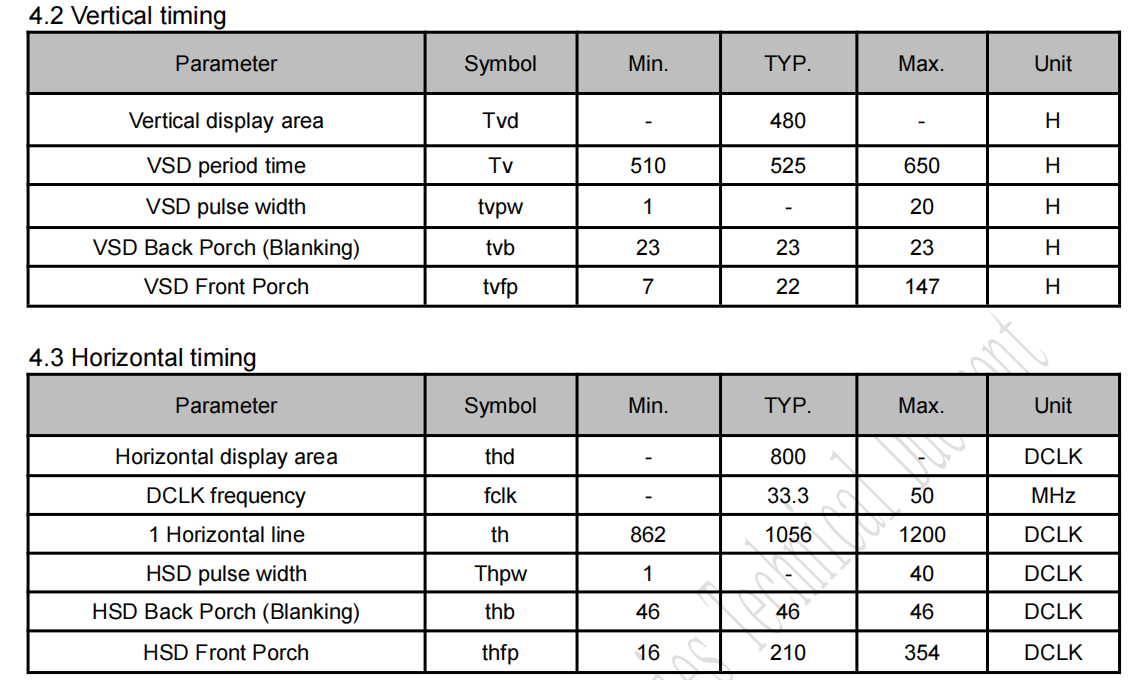

导致该问题的原因可能是 REFCLK 频率和 DSI 视频数据通道的确切频率不匹配。 DSI 源设置为什么 DSI 时钟频率? 是否也用于精确的 32MHz LVDS 时钟输出?

此致、

Ikram