器件型号: SN65DSI84

我在此处开启了一个新主题、我们可以在其中直接与客户讨论:

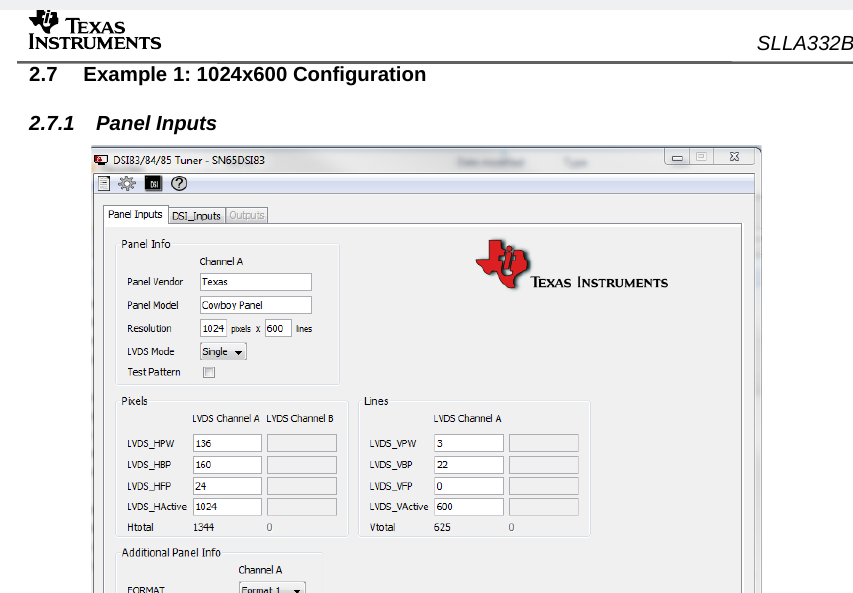

参考图如下所示:

- 线时间同步到同步 26.880us

- 基于实际 DSI Ch*CLK 的数据突发时间和 6.504us 的数据吞吐量

在德州仪器 (TI) 的示例中、LVDS 和 mipi 时序差别很大、与到目前为止的响应相矛盾、在这两个时序中、响应必须准确且相应。

根据上述时间表、在第二个系列的第一封电子邮件中注明。

我所指的应用手册中的示例是否清晰明了?

谢谢、祝大家愉快。

此致、

Fabio

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

器件型号: SN65DSI84

我在此处开启了一个新主题、我们可以在其中直接与客户讨论:

参考图如下所示:

在德州仪器 (TI) 的示例中、LVDS 和 mipi 时序差别很大、与到目前为止的响应相矛盾、在这两个时序中、响应必须准确且相应。

根据上述时间表、在第二个系列的第一封电子邮件中注明。

我所指的应用手册中的示例是否清晰明了?

谢谢、祝大家愉快。

此致、

Fabio

尊敬的 Fabio:

应用手册中 1024x600 的示例在此处未准确显示线时间要求。 此 E2E 显示了线时间的示例: 【常见问题解答】SN65DSI84:SN65DSI84 的线时间

您可以使用此分辨率指南来计算所需的输入:【常见问题解答】SN65DSI84:SN65DSI83、SN65DSI84 和 SN65DSI85 解决方案指南

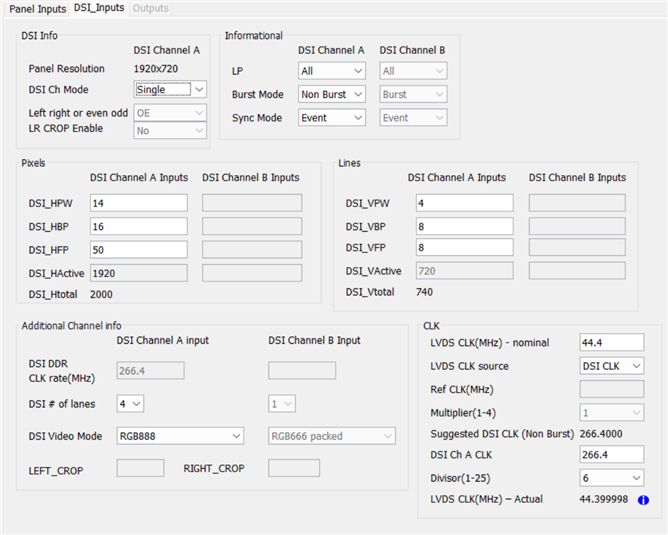

数据突发时间与同步到 SYNC 的线时间不同。

示例:

DSI84 的主要考虑因素将是 LVDS 输出针对双 LVDS 通道进行分离、而 LVDS 时钟将是像素时钟速率的一半(如分辨率指南中所示)。

因此、请相应地对 DSI 输入分辨率进行编程。 以下是 E2E 的另一个示例: RE:SN65DSI83:支持

请注意、由于双路 LVDS 输出用于 DSI84、因此 LVDS 水平时序是 DSI 输入的一半:

如果您使用 线时间 E2E 示例、您会发现 DSI 输入和 LVDS 输出的线时间匹配。

总之、请对 DSI 输入分辨率(水平/垂直总计,活动,消隐)进行编程、以满足面板 LVDS 要求。 对于具有双 LVDS 的 DSI84、水平时序将在 LVDS 通道之间分配(也在 DSI 调谐器 GUI 中注明)。

这是否有任何问题? 客户系统中的 DSI 源是否无法针对确切的显示时序进行编程?

此致、

Ikram