Other Parts Discussed in Thread: TCAN4550, TCAN4551-Q1

https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1579156/tcan4551-q1-spi-speed

器件型号: TCAN4551-Q1

主题中讨论的其他器件: TCAN4550、

尊敬的专家:

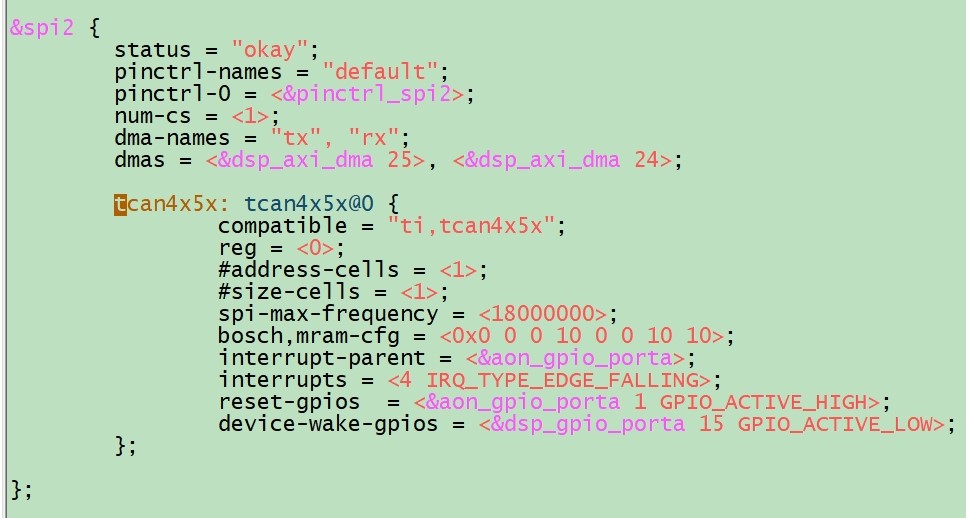

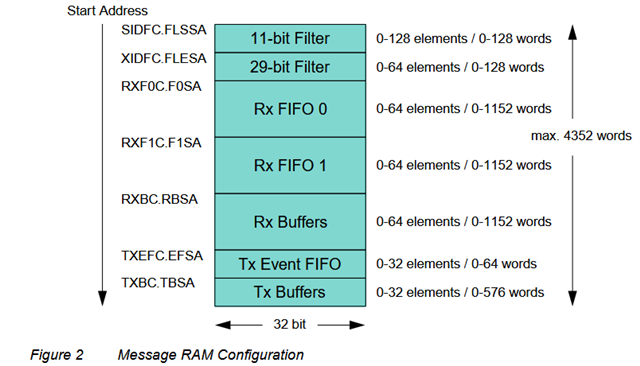

客户将遇到“写入:无缓冲区空间可用“错误、此时 Linux 和 PC 每 100ms 通过 TCAN4551 交换一次消息。 以下是客户 X5M Linux 平台 DTS 配置。 SPI 速度为 18MHz。 有什么问题吗?