Other Parts Discussed in Thread: TCAN4551-Q1

器件型号: TCAN4551-Q1

尊敬的团队:

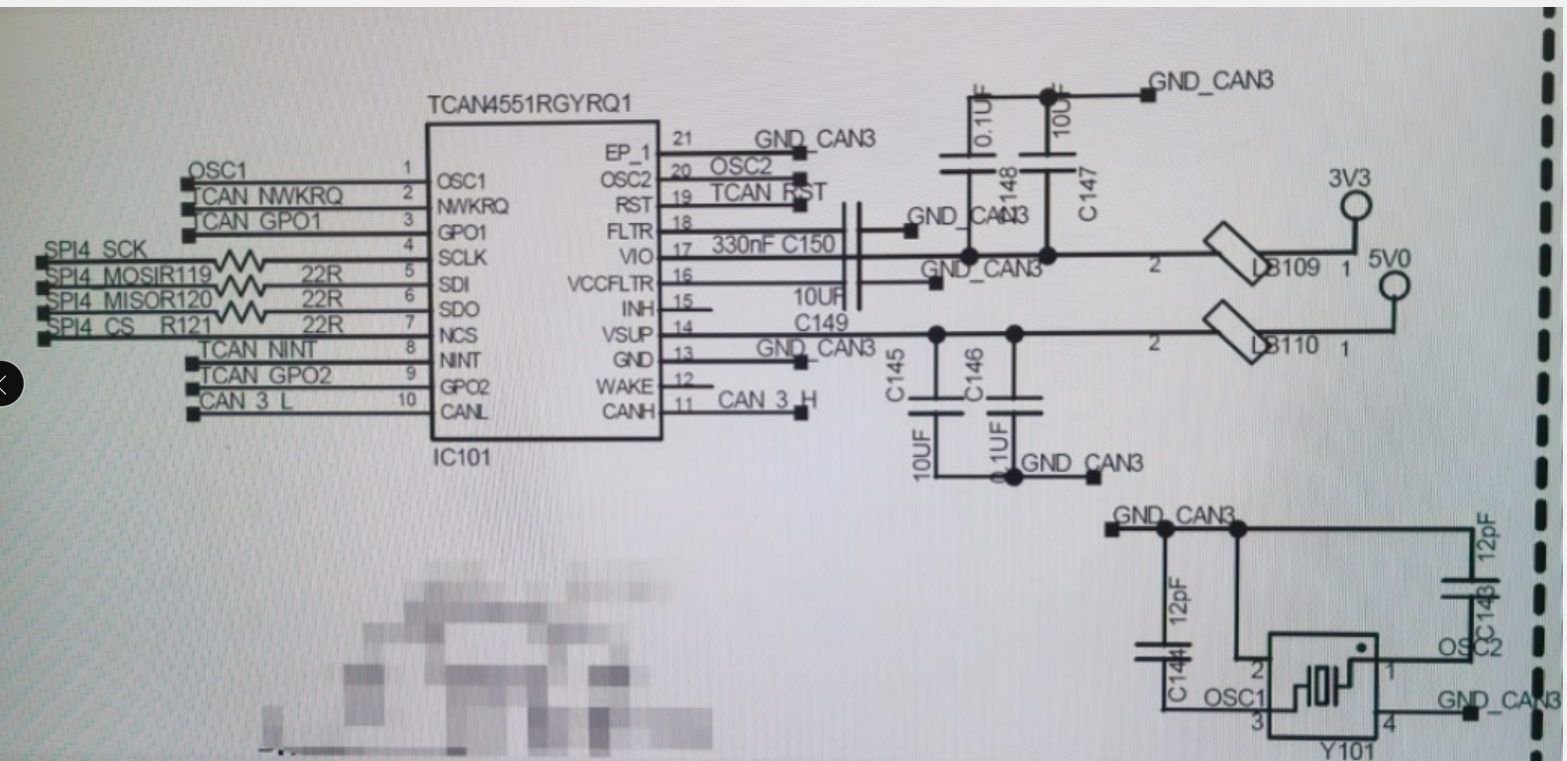

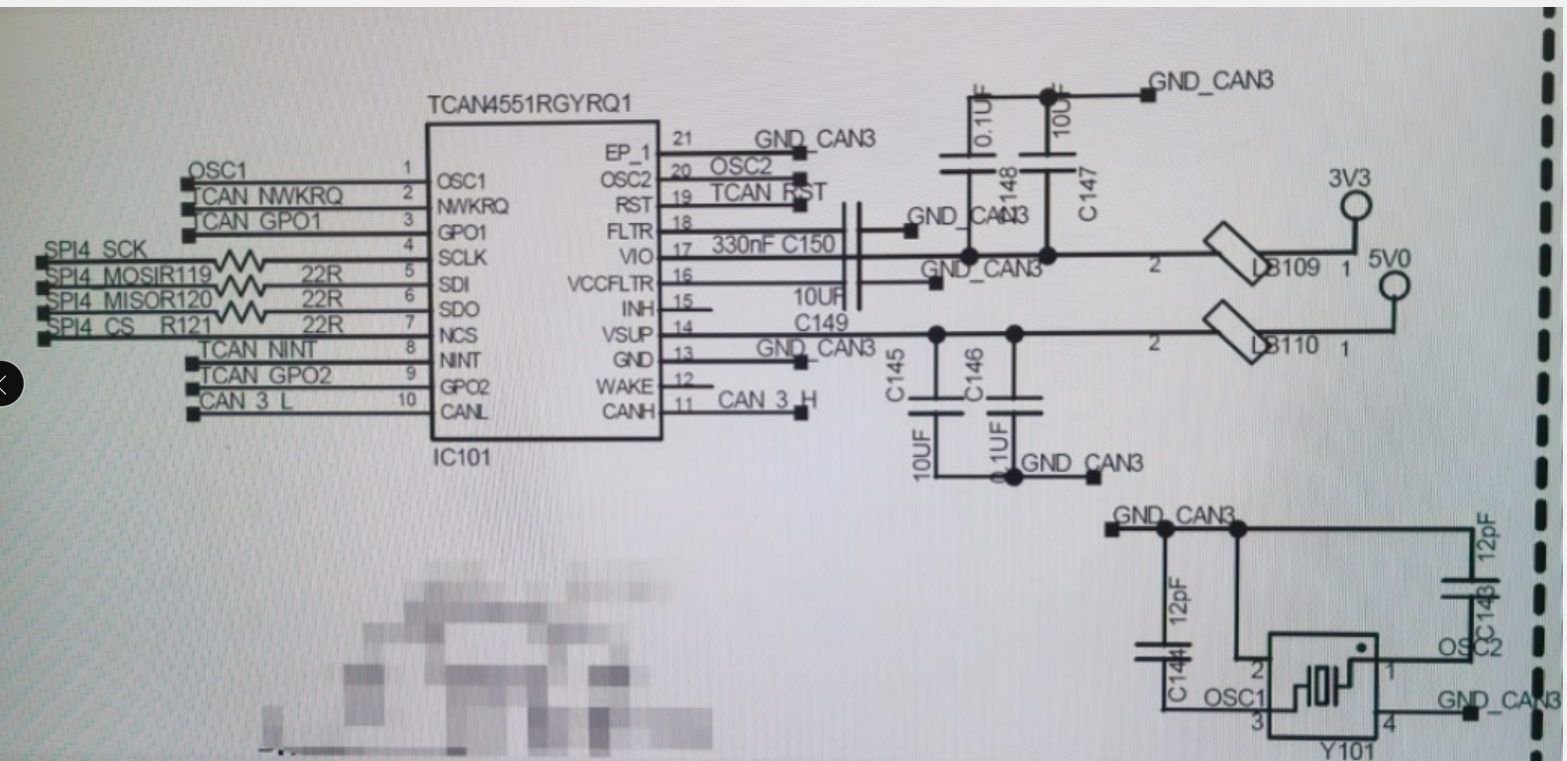

您能帮助检查以下原理图并分享您的意见吗? 是否有必要在 TCAN4551-Q1 应用上添加 40M 晶体振荡器? 此外、如果我们要读取器件 ID、是否可以采取或仅遵循 SPI 读取的任何特殊操作?

谢谢。

BRS。

Frank

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: TCAN4551-Q1

器件型号: TCAN4551-Q1

尊敬的团队:

您能帮助检查以下原理图并分享您的意见吗? 是否有必要在 TCAN4551-Q1 应用上添加 40M 晶体振荡器? 此外、如果我们要读取器件 ID、是否可以采取或仅遵循 SPI 读取的任何特殊操作?

谢谢。

BRS。

Frank

您好 Frank、

是否有必要在 TCAN4551-Q1 应用上添加 40M 晶体振荡器?

是的、您需要连接到 OSC1/2 引脚的晶体或单端时钟。 该时钟源直接控制数字内核和 MCAN 控制器。

此外、如果我们要读取器件 ID、任何需要执行或只是遵循 SPI Read 的特殊操作都没关系?

在 VSUP 和 VIO 电源轨打开并处于建议的工作范围内后、可以对器件 ID 寄存器进行 SPI 读取。

我已经审查了原理图、并有以下注释和观察结果:

- VSUP 电源的最小值为 5.5V、并且器件不会直接由 5.0V 电源供电运行。 内部 5V LDO 需要一些余量电压、因此 VSUP 必须大于 5.5V。

-建议在 OSC1 引脚和晶体之间使用一个串联电阻器、以帮助优化时钟电路以实现稳定运行。 另请查看 TCAN455x 时钟优化和设计指南应用报告 (链接)、了解更多信息。 可以添加一个 0 欧姆电阻器、如有必要、稍后根据进一步优化测试更改该值。

- VSUP、VIO 和 VCCOUT 上的去耦电容器看起来正确。

-如果不使用 WAKE 引脚、它必须连接到 GND 或 VSUP、并且不应悬空。

-没有显示任何上拉或下拉电阻器。 nINT 和 GPO2 引脚为开漏引脚、需要一个连接到 VIO 的上拉电阻器。 nWKRQ 可配置为开漏、需要在 VIO 上连接一个上拉电阻器。

- RST 引脚为高电平有效,因此它需要保持低电平才能正常运行,只有高电平脉冲才能创建复位事件。

此致、

Jonathan