“线程:测试, ALP”中讨论的其它部件

您好 TI 支持者,

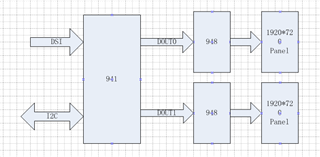

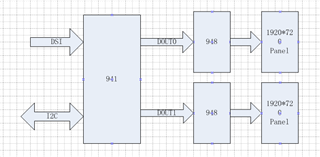

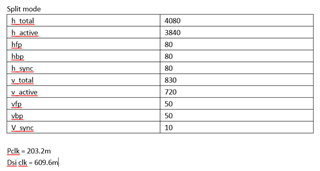

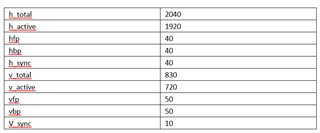

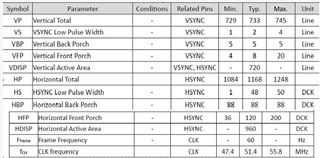

1。 941->2 DES 948 -> 2 1920*720面板 ,如下所述

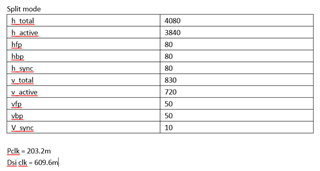

2,面板规格

3.注册配置

e2e.ti.com/.../2311.splitter-mode-port1.txt

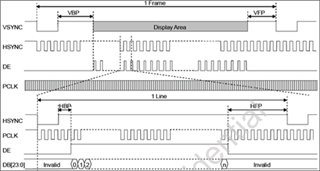

4. 941 DSI 正时

请帮助 检查 分离器模式配置,谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好 TI 支持者,

1。 941->2 DES 948 -> 2 1920*720面板 ,如下所述

2,面板规格

3.注册配置

e2e.ti.com/.../2311.splitter-mode-port1.txt

4. 941 DSI 正时

请帮助 检查 分离器模式配置,谢谢。

洛根:

这是一个紧迫的项目。 作为单 LCD 正时的跟踪,分离器模式 PG 可以显示色条

,

,

但使用超帧计时,分离器模式 PG 无法 工作。 941 reg dump e2e.ti.com/.../split941.txt

您好,建林

感谢您提供更多信息。

如果它在 PatGen 模式下工作,则这是超帧设置问题或输入视频问题。

我已经检查了脚本和寄存器转储,但设置脚本可能存在问题。

在脚本中,配置了 DSI 端口0和端口1。 您是否可以共享应用程序的完整 DSI 系统详细信息,以便我可以确保代码配置正确? 车道计数,港口计数,DSI 时钟模式等?

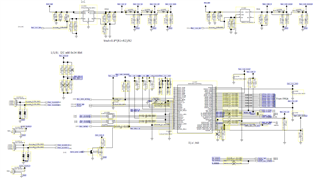

您还能提供示意图吗?这样我就可以查看腕带设置了吗?

下面是对称拆分示例。

# 3840x720@60 Symmetric Split Example - 2x 1920x720@60 # Video 0 and Video 1 Parameters: # HACT = 1920 # HFP = 64 # HSYNC = 32 # HBP = 32 # VACT = 720 # VFP = 45 # VSYNC = 8 # VBP = 8 # PCLK = 96MHz # DSI Superframe Dimensions: # HACT = 3840 # HFP = 128 # HSYNC = 64 # HBP = 64 # VACT = 720 # VFP = 45 # VSYNC = 8 # VBP = 8 # PCLK = 192MHz # DSI clock = 576MHz # DSI Lane Speed = 1152Mbps/lane # 4 Lanes DSI # DSI input port 0 import time UB941AS = 0x18 board.WriteI2C(UB941AS,0x01,0x02) # Reset time.sleep(0.1) board.WriteI2C(UB941AS,0x01,0x08) # Disable DSI board.WriteI2C(UB941AS,0x1E,0x01) # Select port 0 board.WriteI2C(UB941AS,0x4F,0x8C) # 4 Lane Mode continuous clock board.WriteI2C(UB941AS,0x5B,0x07) # Splitter mode board.WriteI2C(UB941AS,0x40,0x04) # TSKIP_CNT board.WriteI2C(UB941AS,0x41,0x05) # TSKIP_CNT board.WriteI2C(UB941AS,0x42,0x40) # TSKIP_CNT board.WriteI2C(UB941AS,0x56,0x80) # L/R Pixel Processing board.WriteI2C(UB941AS,0x32,0x80) # Set 2D Line Size 1920 board.WriteI2C(UB941AS,0x33,0x07) # board.WriteI2C(UB941AS,0x1E,0x01) # Select port 0: 1920x720 board.WriteI2C(UB941AS,0x36,0x00) board.WriteI2C(UB941AS,0x37,0x80) # X Start = 0 board.WriteI2C(UB941AS,0x38,0x7F) board.WriteI2C(UB941AS,0x39,0x07) # X Stop = 1919 board.WriteI2C(UB941AS,0x3A,0x00) board.WriteI2C(UB941AS,0x3B,0x00) # Y Start = 0 board.WriteI2C(UB941AS,0x3C,0xCF) board.WriteI2C(UB941AS,0x3D,0x02) # Y Stop = 719 board.WriteI2C(UB941AS,0x1E,0x02) # Select port 1: 1920x720 board.WriteI2C(UB941AS,0x36,0x00) board.WriteI2C(UB941AS,0x37,0x80) # X Start = 0 board.WriteI2C(UB941AS,0x38,0x7F) board.WriteI2C(UB941AS,0x39,0x07) # X Stop = 1919 board.WriteI2C(UB941AS,0x3A,0x00) board.WriteI2C(UB941AS,0x3B,0x00) # Y Start = 0 board.WriteI2C(UB941AS,0x3C,0xCF) board.WriteI2C(UB941AS,0x3D,0x02) # Y Stop = 719 board.WriteI2C(UB941AS,0x40,0x10) # Init DSI Clock Settings (From Section 10.2 of datasheet) board.WriteI2C(UB941AS,0x41,0x86) # Init DSI Clock Settings (From Section 10.2 of datasheet) board.WriteI2C(UB941AS,0x42,0x0A) # Init DSI Clock Settings (From Section 10.2 of datasheet) board.WriteI2C(UB941AS,0x41,0x94) # Init DSI Clock Settings (From Section 10.2 of datasheet) board.WriteI2C(UB941AS,0x42,0x0A) # Init DSI Clock Settings (From Section 10.2 of datasheet) board.WriteI2C(UB941AS,0x01,0x00) #Release DSI

此致,

洛根

洛根:

添加原理图和完整的 SerDes 初始化代码,请帮助检查,谢谢。

(ti941_addr,0x01,0x08);//禁用 DSI

(ti941_addr,0x1E,0x01);//选择 FPD-Link III 端口0

(ti941_addr,0x03,0x9A);//启用 I2C_passthrough,FPP-Link III 端口0

(ti941_addr,0x17,0x9E);

(ti941_addr,0x06,0x59);

(ti941_addr,0x07,0x30);

(ti941_addr,0x08,0x32);

(ti941_addr,0x0E,0x03);

(ti941_addr,0x0F,0x03);

(ti941_addr,0x4F,0x8C);//设置 DSI_continued_clock,4个通道,DSI 端口0

(ti941_addr,0x5B,0x07);//强制分路器模式

(ti941_addr,0x56,0x80);//启用左/右3D 处理以允许超帧拆分

(ti941_addr,0x1E,0x02);//选择 FPD-Link III 端口1

(ti941_addr,0x03,0x9A);//启用 I2C_passthrough,FPD-Link III 端口1

(ti941_addr,0x17,0x9E);

(ti941_addr,0x06,0x61);

(ti941_addr,0x07,0x30);

(ti941_addr,0x08,0x34);

(ti941_addr,0x0E,0x03);

(ti941_addr,0x0F,0x03);

(ti941_addr,0x4F,0x8C);//设置 DSI_continued_clock,4个通道,DSI 端口1

(ti941_addr,0x5B,0x07);//强制分路器模式

(ti941_addr,0x56,0x80);//启用左/右3D 处理以允许超帧拆分

(ti941_addr,0x32,0x80);//将行大小设置为1280 (LSB)

(ti941_addr,0x33,0x07);//将行大小设置为1280 (MSB)

(ti941_addr,0x1E,0x01);//选择 FPD-Link III 端口1

(ti941_addr,0x360x00);//将作物起点 X 位置设置为0 (LSB)

(ti941_addr,0x37,0x80);//将裁剪开始 X 位置设置为0 (MSB)并启用裁剪

(ti941_addr,0x38,0x7F);//将作物停止 X 位置设置为1919 (LSB)

(ti941_addr,0x39-07);//将作物停止 X 位置设置为1919 (MSB)

(ti941_addr,0x3A,0x00);//将作物开始 Y 位置设置为0 (LSB)

(ti941_addr,0x3B,0x00);//将作物开始 Y 位置设置为0 (MSB)

(ti941_addr,0x3C,0xCF);//将作物停止 Y 位置设置为719 (LSB)

(ti941_addr,0x3D,0x02);//将裁剪停止 Y 位置设置为719 (MSB)

(ti941_addr,0x1E,0x02);//选择 FPD-Link III 端口1

(ti941_addr,0x360x00);//将作物起点 X 位置设置为0 (LSB)

(ti941_addr,0x37,0x80);//将裁剪开始 X 位置设置为0 (MSB)并启用裁剪

(ti941_addr,0x38,0x7F);//将作物停止 X 位置设置为1919 (LSB)

(ti941_addr,0x39-07);//将作物停止 X 位置设置为1919 (MSB)

(ti941_addr,0x3A,0x00);//将作物开始 Y 位置设置为0 (LSB)

(ti941_addr,0x3B,0x00);//将作物开始 Y 位置设置为0 (MSB)

(ti941_addr,0x3C,0xcF);//将作物停止 Y 位置设置为719 (LSB)

(ti941_addr,0x3D,0x02);//将裁剪停止 Y 位置设置为719 (MSB)

(ti941_addr,0x40,0x04);//选择 DSI 端口0数字寄存器

(ti941_addr,0x41,0x05);//选择 DPHY_SKIP 计时寄存器

(ti941_addr,0x42,0x18);//写入300 MHz DSI 时钟频率的 SKIP_CNT 值

(ti941_addr,0x01,0x00);//启用 DSI

(ti941_addr,0x1E,0x01);//端口0

(ti948地址,0x1f,0x05);/GPIO3

(ti941_addr,0x1E,0x01);

(ti941_addr,0x03,0x9a);

(ti941_addr,0x00、0x34);

(ti941_addr,0x1E,0x02);

(ti941_addr,0x03,0x9a);

(ti941_addr,0x1E,0x07);

(ti948,2nd,addr,0x1f,0x05);

您好,建林

在脚本中,DSI 端口0和端口1均已配置。~ 您是否可以共享应用程序的完整 DSI 系统详细信息,以便我可以确保代码配置正确? 车道计数,港口计数,DSI 时钟模式等?请对上述 DSI 参数进行评论吗? 正确的脚本配置取决于 DSI 源和配置,因此我首先要确保设备处于正确的模式,并且脚本中的其他 DSI 计时(如 TSKIP 计数等)正在正确配置(并通过 modeSel 引脚进行绑定)。 根据示意图,似乎只使用一个 DSI 端口和4个通道;这是正确的吗?

[引用 userid="505472" url="~ë/support/interface-group/interface/f/interface-forum/1068372/ds90ub941as-Q1-please-check-sex分割 器模式配置/3960760#3960760"]使用单 LCD DSI 视频信号 ,pclk = 101m ,DSI clk = 303m,分离器模式 pg 可以工作。

但使用超帧 DSI 视频信号 pclk =203m ,DSI clk =609m,分离器模式 pg 无法工作。

[/引用]您能否进一步澄清每次测试的差异? 您是否认为在 DSI 时钟模式和 PatGen 模式下,当输入303MHz (101MHz PCLK)时,PatGen 在两个显示器上都工作,但当 DSI 时钟为609MHz (203Mhz PCLK)时,显示器不工作? 我们能否先验证设备是否处于 分离器模式且未在复制模式下配置?

您是否可以共享您用于配置 PatGen 的脚本,或者该脚本是使用 ALP 设置的?

此致,

洛根

您好,建林

如果我为您的配置重新创建941脚本,您是否可以运行它,而不是当前使用的脚本? 如果可以,我想从一个新的脚本开始。

至于您对使用单显示器 PCLK 的 patgen 的最初问题,这是因为每个 FPD 端口都有自己的分路器/独立模式下的 patgen 块。 因此,在执行外部时钟 DSI 参考时钟模式时,只使用单个 PCLK DSI 速率。 这是有道理的吗?

此致,

洛根

洛根:

感谢你的回复。

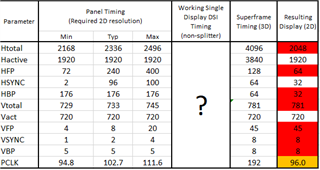

今天,我使用 RevB_941AS_superframe _Calc.xlsm 来配置3840*720分离器模式设置。

我尝试使用 DSI 时钟620M 和660m,生成941的设置,并将620M/660m DSI 输入到941,对于不同的 DSI 时钟,只有 TSKIP CNT 值不同,

但仍然无法显示。 我发现 DSI 时钟会影响分离器模式链路。

我在工具中找不到任何门廊计时设置。941的设置是否需要

考虑液晶屏的时间?

请帮助为 我们的配置创建941脚本,谢谢

您好,建林

您使用的是连续还是非连续时钟模式? 我在评论中看到脚本说不连续,但设置是否连续?

我发现脚本有几个问题,并在下面重新上传:

e2e.ti.com/.../941_5F00_Y_2D00_Split.py

如果仍然不起作用,请再次提供主页和 DSI 页的寄存器转储。

此致,

洛根

洛根:

使用您的设置,但仍无法显示,输入 DSI 为620M。

有很多 DSI 错误,注册转储如下,请帮助检查,谢谢。

洛根:

另一个卸载是卸捆 PG 底座分离器模式 PG 成功设置。

您好,建林

[引用 userid="272407" url="~ë/support/interface-group/interface/f/interface-forum/1068372/ds90ub941as-Q1-please-check-suser-mode-configuration/3964673#3964673]]]\n 您是否使用连续或非连续时钟模式? 我在评论中看到脚本说不连续,但设置是否连续?您能否澄清上述问题以确保脚本正确设置正确模式?

洛根

洛根,í a,您好

有 一条信息可供您了解。 单屏模式(DSI ->941 ->主端口948 ->面板)可以 正常显示。

对于分离器模式配置:

1 941配置根据 脚本设置更改为分离器模式。

2分路器模式 PG 可以显示,关闭 PG,直接测试 DSI 视频,分路器模式无法显示。

3 DSI 视频信号从1920*720更改为3840*720,线路空白*2。

这个问题阻碍了项目的实施,请给我很多支持 ,非常感谢。

您好,建林

是否可以验证您尝试执行的脚本是否 是我所附加的941_YSplit.py?

您是否有 DSI 分析软件来验证数据包结构和视频定时?

如果您看到 DSI 错误,这可能会导致您看到的问题。 我现在更仔细地看寄存器转储,并将在今天下午晚些时候提供反馈。

根据我对您的解释的理解:

您能否验证 DSI CLK 速率是否从单显示器 PCLK 更改为2xPCLK? 如前所述,有两个单独的 PG 块;因此,DSI 时钟可以用于一个显示屏,但仍会输出两个显示屏。 但是,当切换到分离器模式时,DSI CLK 需要从 1920*720更新到3840*720 DSI CLK。

如果单显示器工作正常,并且 patgen 分离器模式工作,则可能是超帧输入或配置导致问题。 请确认您正在使用我提供的先前附加脚本,然后我们可以继续验证 DSI 输入。

此致,

洛根

洛根,í a,您好

感谢你的回复。

1我使用 了 TH 941_YSplit 设置,拆分器模式无法显示

2 941单显示器工作正常(端口0?)

是,941端口0单显示器可以正常工作。

3分离器模式 DSI 时钟/包是1920*720的两倍

4我们使用 了振荡器打开 mipi 解码器工具来分析 DSI 输入,存在一些 mipi 错误,,但仍可以解码输入视频图像。

洛根:

感谢你的回复。

当从内部时钟更改为 DSI CLK 时,我确认分离器 PG 工作成功。

我发现 DSI 错误 是 由 DSI 时钟,DSI 时钟更高,更多 DSI 状态错误引起的。

附件为941 948 reg dump,DSI 输入540M。

//DSI 输入540M

*** DSI0 IA 注册***

0x01:0x00

0x02:0x00

0x03:0x1d

0x04:0x10

0x05:0x1a

0x06:0x00

0x07:0x00

0x08:0x00

0x09:0x00

0x0A:0x00

0x0B:0x00

0x0C:0x00

0x0D:0x00

0x0E:0x00

0x0F:0x7f

0x10:0x00

0x11:0x00

0x12:0x00

0x13:0x04

0x14:0x00

0x15:0x07

0x16:0x00

0x17:0x00

0x18:0x00

0x19:0x00

0x1a:0x00

0x1b:0x00

0x1c:0x00

0x1d:0x00

0x1E:0x00

0x1f:0x00

0x20:0x7f

0x21:0x00

0x22:0xff

0x23:0x7f

0x24:0x00

0x25:0x00

0x26:0x00

0x27:0x00

0x28:0x01

0x29:0x01

0x2a:0x00

0x2b:0x00

0x2C:0x02

0x2D:0x00

0x2E:0x00

0x2F:0x00

0x30:0x00

0x31:0x20

0x32:0x00

0x33:0x04

0x34:0x00

0x35:0x20

0x36:0x00

0x37:0x00

0x38:0x00

0x39:0x00

0x3a:0x02

0x3B:0x03

//DSI 时钟660m

*** DSI0 IA 注册***

0x01:0x00

0x02:0x00

0x03:0x1d

0x04:0x10

0x05:0x20

0x06:0x00

0x07:0x00

0x08:0x00

0x09:0x00

0x0A:0x00

0x0B:0x00

0x0C:0x00

0x0D:0x00

0x0E:0x00

0x0F:0x7f

0x10:0x16

0x11:0x14

0x12:0x16

0x13:0x16

0x14:0x00

0x15:0x0d

0x16:0x00

0x17:0x00

0x18:0x00

0x19:0x00

0x1a:0x00

0x1b:0x00

0x1c:0x00

0x1d:0x00

0x1E:0x00

0x1f:0x00

0x20:0x7f

0x21:0x00

0x22:0xff

0x23:0x7f

0x24:0x00

0x25:0x00

0x26:0x00

0x27:0x00

0x28:0x05

0x29:0xff

0x2a:0x3e

0x2b:0x8d

0x2C:0x06

0x2D:0x02

0x2E:0x00

0x2F:0x00

0x30:0x00

0x31:0x20

0x32:0x00

0x33:0x04

0x34:0x00

0x35:0x20

0x36:0x00

0x37:0x00

0x38:0x00

0x39:0x00

0x3a:0x02

您好,建林

本941 DSI 启动指南提供了有关验证 DSI 输入的详细说明: https://www.ti.com/lit/an/snla356/snla356.pdf

另一件要验证的事情是 DSI 时钟的 DSI 抖动,如本常见问题解答文章: DSI/REFCLK 抖动测量中所述

此致,

洛根

洛根:

DSI 输入 mipi CTS 测试中存在一些问题。 而 mipi clk 抖动 129.8pfs > 100pfs,

这些问题可能会导致 分离器模式不显示,我们将立即解决这些问题。

非常感谢。

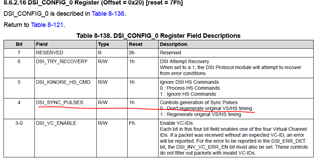

洛根:

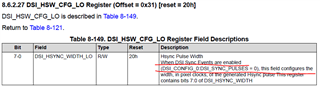

另一个问题是,我们的 DSI 输入格式是具有同步事件数据包结构的非突发模式。

请参阅 snla356.pdf“因为事件模式不利用 HSE 和 VSE 数据包来定义 HSYNC /VSYNC 的下缘

必须对序列化器进行编程,以便使用 DSI_HSW_CFG 和生成所需的同步宽度

DSI_VSW_CFG 寄存器。"

我按照以下方式配置 DSI reg,这是否正确?

(ti941_addr,0x40,0x04);//选择 DSI 端口0数字寄存器

(ti941_addr,0x41,0x05);//选择 DPHY_SKIP 计时寄存器

(ti941_addr,0x42,0x1c);//写入300 MHz DSI 时钟频率的 SKIP_CNT 值

(ti941_addr,0x41,0x20);

(ti941_addr,0x42,0x6f);//DSI_SYNC_Pulses 0

(ti941_addr,0x41,0x30);

(ti941_addr,0x42,0x00);//HSYNC

(ti941_addr,0x41,0x31);

(ti941_addr,0x42,0x40);//HSYNC 64

(ti941_addr,0x41,0x32);

(ti941_addr,0x42,0x00);//vsync

(ti941_addr,0x41,0x33);

(ti941_addr,0x42,0x08);//vsync 8.

您好,建林

[引用 userid="505472" url="~ë/support/interface-group/interface/f/interface-forum/1068372/ds90ub941as-Q1-please-check-sexpress-mode-configuration/3985579#3985579"]由于项目被拖延了很长时间,是否有办法加快项目的进度?

上海 TI 是否有任何现场支持?

[/引用]很抱歉,我们在上海没有 FPD-Link 的本地支持。 您是否有当地的 TI 现场应用工程师? 如果我们能为美国和上海找到共同的时间,他/她可能能够帮助调试和/或促进实时调试。

请提供下面要求的所有信息,以帮助找出根本原因并有效解决问题。 自调试开始以来,许多设置和结果都已声明/更改,我希望确认您的理解并确保我们位于同一页。

请提供以下信息:

我希望将调试工作集中在两个方面:

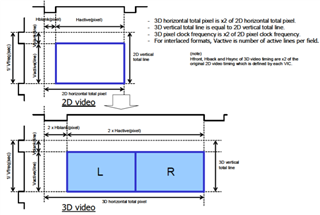

关于您对 DSI 超帧,941和948计时的问题。 DSI 超帧应基于所需的显示视频时钟,如下所述:

此致,

洛根

洛根:

感谢你的回复。

确认信息:

1面板正时参数

2 DSI 超帧计时参数和时钟参数

# DSI 超帧尺寸:

#现金统转=3840

# HFP = 128

# HSYNC = 64

# HBP = 64

# VACT = 720

编号 VFP = 45

# VSYNC = 8

# VBP = 8

# PCLK = 192 MHz

# DSI 时钟= 576MHz

# DSI 车道速度= 1152Mbps/车道

4号通道 DSI

# DSI 输入端口0

3 DSI 输入仅支持同步事件数据包结构的非突发模式。我的当前脚本如下所指。

Board.WriteI2C (UH941AS,0x01,0x08)//禁用 DSI

Board.WriteI2C (UH941AS,0x1E,0x01)//选择 FPD-Link III 端口0

Board.WriteI2C (UH941AS,0x4F,0x8C)//设置 DSI_continuous_clock,4个通道,DSI 端口0

Board.WriteI2C (UH941AS,0x5B,0x07)//强制分路器模式

Board.WriteI2C (UH941AS,0x56,0x80)//启用左/右3D 处理以允许超帧拆分

Board.WriteI2C (0x1E,0x01)//选择 FPP-Link III 端口1

Board.WriteI2C (UH941AS,0x32,0x80) #set IMG_LINE_SIZE

Board.WriteI2C (UH941AS,0x33,0x07) #set IMG_LINE_SIZE

Board.WriteI2C (UH941AS,0x36,0x00) #设置作物开始 X 位置(LSB)

Board.WriteI2C (UH941AS,0x37,0x80 )#设置作物开始 X 位置(MSB)

Board.WriteI2C (UH941AS,0x38,0x7F) #设置作物停止 X 位置(LSB)

Board.WriteI2C (UH941AS,0x39,0x07) #设置作物停止 X 位置(MSB)

Board.WriteI2C (UH941AS,0x3A,0x00) #设置作物开始 Y 位置(LSB)

Board.WriteI2C (UH941AS,0x3B,0x00) #设置作物开始 Y 位置(MSB)

Board.WriteI2C (UH941AS,0x3C,0xCF) #设置作物停止 Y 位置(MSB)

Board.WriteI2C (UH941AS,0x3D,0x02)

Board.WriteI2C (UH941AS,0x1E,0x02)//选择 FPD-Link III 端口1

Board.WriteI2C (UH941AS,0x32,0x80) #set IMG_LINE_SIZE

Board.WriteI2C (UH941AS,0x33,0x07) #set IMG_LINE_SIZE

Board.WriteI2C (UH941AS,0x36,0x00) #设置作物开始 X 位置(LSB)

Board.WriteI2C (UH941AS,0x37,0x80 )#设置作物开始 X 位置(MSB)

Board.WriteI2C (UH941AS,0x38,0x7F) #设置作物停止 X 位置(LSB)

Board.WriteI2C (UH941AS,0x39,0x07) #设置作物停止 X 位置(MSB)

Board.WriteI2C (UH941AS,0x3A,0x00) #设置作物开始 Y 位置(LSB)

Board.WriteI2C (UH941AS,0x3B,0x00) #设置作物开始 Y 位置(MSB)

Board.WriteI2C (UH941AS,0x3C,0xCF) #设置作物停止 Y 位置(MSB)

Board.WriteI2C (UH941AS,0x3D,0x02)

//在 DSI Port0上编程 TSKIP_CNT DSI 参数

Board.WriteI2C (UH941AS,0x40,0x04)//选择 DSI 端口0数字寄存器

Board.WriteI2C (UH941AS,0x41,0x05)//选择 DPHY_SKIP 计时寄存器

用于580 MHz DSI 时钟频率的 Board.WriteI2C (UH941AS,0x42,0x1c)//Write SKIP_CNT 值

Board.WriteI2C (UH941AS,0x41,0x04)//H_沉 降

Board.WriteI2C (UH941AS,0x42,0x10)

Board.WriteI2C (UH941AS,0x01,0x00)//启用 DSI

Board.WriteI2C (0x1E,0x07)

确认信息(续):

4 DSI 验证详细信息和测试结果。 DSI CTS 测试通过,抖动129.8pfs @ DSI 输入时钟580m

[引用 userid="272407" url="~ë/support/interface-group/interface/f/interface-forum/1068372/ds90ub941as-Q1-please-check-sexperse-mode-configuration/3986575#3986575"]我们的工具无法确认 DSI 计时。DSI 错误尚未解决。

[引用 userid="272407" url="~/support/interface-group/interface/f/interface-forume/1068372/ds90ub941as-Q1-please-check-sexiter-mode-configuration/3986575#3986575"]寄存器941个主页和 DSI 页的转储 ~用户名="272407" url="支持/接口-组/接口/f/interface-forum/1068372/ds90ub941as - Q1-please check - s分流 器-模式-配置/3986575#3986575"]以下测试模式的状态摘要:单端口0 DSI 输入成功,端口1 DSI 未测试。

[引用 userid="272407" url="~/support/interface-group/interface/f/interface-forum/1068372/ds90ub941as-Q1-please-check-spliter-mode-configuration/3986575#3986575"]分路器模式,DSI 输入-不成功“不成功,”面板为黑色。

[引用 userid="272407" url="~/support/interface-group/interface/f/interface-forum/1068372/ds90ub941as-Q1-please check-spliter-mode-configuration/3986575#3986575"]分路器模式,内部 PatGen,DSI 时钟模式-成功吗?分离器模式内部 PatGen 成功,DSI 时钟模式失败,因为我只将941端口0重新格式0x56更改为0,941仍是内部时钟。

当941在分离器模式下工作时,我发现948没有链接,访问948也失败。

洛根,í a,您好

我尝试按照以下步骤配置941计时:

分离器模式内部 PatGen 成功,DSI 时钟(580m)模式 成功。

分离器模式 DSI 时钟模式通道为黑色,948s 链路成功。

//分离器模式948链路成功

(ti941_addr,0x40,0x04);//选择 DSI 端口0数字寄存器

(ti941_addr,0x41,0x05);//选择 DPHY_SKIP 计时寄存器

(ti941_addr,0x42,0x1c);//写入300 MHz DSI 时钟频率的 SKIP_CNT 值

(ti941_addr,0x41,0x03);//沉淀_定时

(ti941_addr,0x42,0x3a);//

(ti941_addr,0x41,0x04);//H_沉 降

(ti941_addr,0x42,0x28);//

您好,建林

很高兴您能锁住448台。

您是否可以对941 GPIO6,GPIO5和 GPIO4引脚进行探头访问? 我们可以尝试将从 DSI 数据包接收到的定时信号映射到输出 DE,HSYNC 和 VSYNC 信号,并对它们进行正确且符合预期的比较。

此致,

洛根

洛根,í a,您好

1 ths_沉 降和 CLK_沉 降解决 了948秒的链路丢失问题,但 DSI 错误仍然存在,单 个 LCD 模式中存在 DSI 错误,且显示成功。

2对于 PatGen 拆分器模式和 DSI 输入拆分器模式,DSI 时钟为580Mhz。TSKIP_CNT 值 0x1c 用于580Mhz。

3寄存器转储如下

4我将在 以后探测单端941 GPIO6,GPIO5和 GPIO4引脚。

非常感谢。

您好,建林

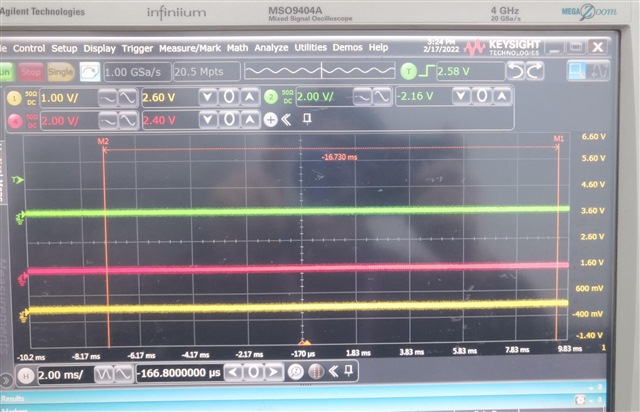

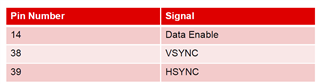

您能否参考本指南以打开调试模式以映射到这些引脚? 很抱歉,我原以为是随附的。 以下说明将引脚14映射到 DE,引脚38映射到 VSYNC,引脚39映射到 HSYNC。 如果您能够获得与前一个示波器显示的类似示波器,并附带所有三个信号,我们可以抽查 DSI 计时以查看其是否正确。 根据寄存器0x5F,每个端口的 PCLK 频率为~97MHz;这似乎是预期的。

e2e.ti.com/.../8171.941AS-Sync-Signal-Extraction-for-Debug-_2800_3_2900_.pdf

我对超帧 DSI 分辨率有担忧。 这似乎违反了您提供的面板计时的最小/最大参数。

此致,

洛根

洛根,í a,您好

1用于单 LCD 和分离器模式的输入 DSI 视频正时,如下所示。

# 3840x720@60对称分屏示例- 2个1920x720@60

#视频0和视频1参数:

#现金统转= 1920

# HFP = 64

# HSYNC = 32

# HBP = 32

# VACT = 720

编号 VFP = 45

# VSYNC = 8

# VBP = 8

# PCLK = 96MHz

# DSI 超帧尺寸:

#现金统转=3840

# HFP = 128

# HSYNC = 64

# HBP = 64

# VACT = 720

编号 VFP = 45

# VSYNC = 8

# VBP = 8

# PCLK = 192 MHz

# DSI 时钟= 576MHz

# DSI 车道速度= 1152Mbps/车道

4号通道 DSI

# DSI 输入端口0

我多次调整 DSI 超帧的视频计时,仍然找不到分流器模式的固定计时。

2根据指南,探测 DE/HSYNC /VSYNC 信号。

单 LCD 模式

分离器模式

您好,建林

三个快速问题可确保我们位于同一页:

对于分路器模式,HS/VS/DE 上没有任何信号这一事实非常可疑。 这意味着没有来自 DSI 数据包的重新生成计时,这很可能是问题的根本原因。

此致,

洛根

洛根:

感谢你的回复。

我们的硬件工程师确认信号 为绿色(DE)\粉红色(HS)\黄色(VS)。

[引用 userid="272407" url="~ë/support/interface-group/interface/f/interface-forum/1068372/ds90ub941as-Q1-please check-soutler-mode-configuration/3990922#3990922"]当将这些计时参数用于具有单显示模式的 DSI 输入模式时,您是否能够成功获得输出数据[引用]?单显示器模式可以成功显示。

单显示器模式和分离器模式的测试步骤相同,确保941在正确模式下工作,具有正确的 DSI 输入 视频,

然后发送命令“i2cset -fY 2 0x1a 0x24 0xb6 b” 。

我有一个问题,对于单显示器模式,引脚38和39 (HS/VS)不能探测单个,但显示成功,

所需的信号(DE/HS/VS)类似于下图?