线程中讨论的其他部件:DP83869, 测试, DP83869EVM

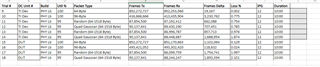

我有一个 DP83869连接到具有 RGMII 的基于 FPGA 的 MAC,我正在使用 Ixia 在设备上发送 UPD 数据包,AM 信号点击 RGMII Rx 和 Ctrl 行。 如果我将其设置为在 RGMII Ctrl 行为0x01时触发,那么我将看到数据包应该位于的巨大间隙,但 MAC 不会接收到数据包。

第二个至下信号是 Rx_Ctrl 行,在有效数据包期间,信号为0x3。 底部信号是 Rx_data 行,在向右的巨大差距期间,数据包应该位于该行,但 PHY 不发送任何数据包,而且 Ctrl 行是0x1,这似乎不正确。

我找不到任何有关 RGMII 标准的信息,因此我不知道这意味着什么,但显然有些事情是不对的。

任何见解都值得赞赏,

雷蒙德