Other Parts Discussed in Thread: MSP430F5510

《线程》中讨论的其他部件:MSP430F5510

TI 您好:

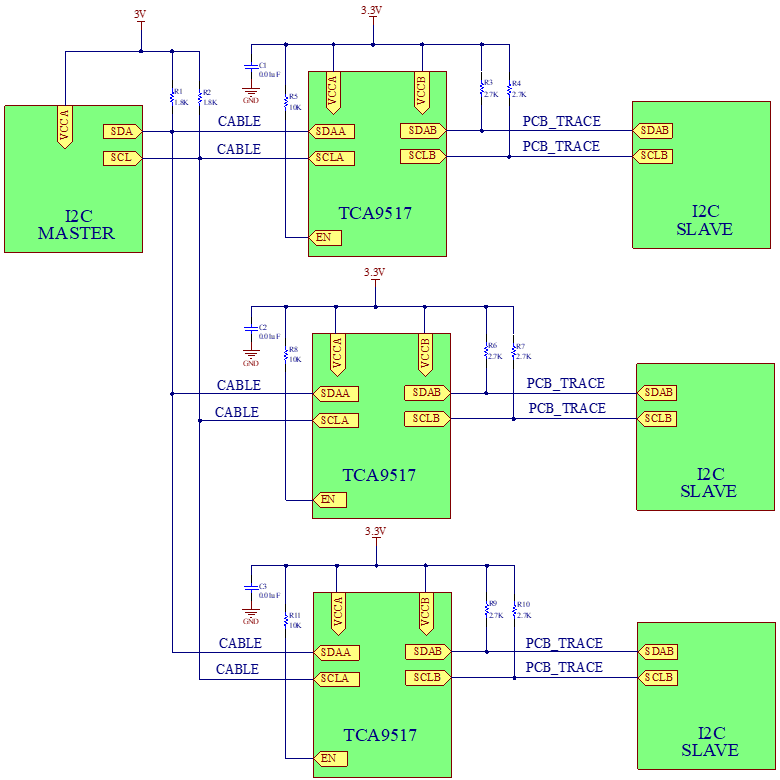

我的公司收购了一款通过电缆使用 I2C 通信协议的产品。 主板和多层板之间的连接是典型的星型应用。 主板和层板之间有一个 I2C 中继器(TCA9517DGKRQ1)。 I2C 主 MCU 位于主板中,I2C 从 MCU 和 I2C 中继器(TCA9517DGKRQ1)位于层板中。

我在上图中发现了2个设计缺陷:

- VCCA 未连接到 A 侧电源电压,VCCA 和 VCCB 被连接到 B 侧电源电压。 TCA9517DGKRQ1芯片应作为电压电平转换器工作,但 VCCA 电源未连接到芯片。

- VCCA 侧附近只有一个去耦电容器。

您能否帮助了解 I2C 总线中继器中的这种错误配置将如何影响 I2C 通信?

系统有多个 I2C 错误。 为了处理某些 I2C 错误,固件会在 I2C 错误后执行重试以重新发送 I2C 数据包。 当 I2C 从控制器保持较低的 SDA 线路时,也会发生 I2C 总线锁定。 这些类型的 I2C 错误是灾难性的,系统在没有电源循环的情况下无法恢复。

我注意到,I2C 信号的异常快速转换会引发 I2C 错误,因为这会影响 I2C 解码器理解线路上数据的能力。 我注意到,I2C 信号的异常快速转换会引发2C 错误,因为这会影响 I2C 解码器正确解码线路上数据的能力。 我使用的是 I2C 总线分析仪和一个示波器,其中内置 I2C 协议插入 A 侧,用于分析和记录 I2C 帧。

与 SDA 保持稳定的高水平相比,从高到低有快速的过渡,并回到高。 在此特定情况下,示波器中的 I2C 解码器在3个数据字节后停止解码。 查看下图中的缩放视图,了解 SDA 线异常快速过渡的详细信息。

我在示意图中发现的唯一问题是我指出的问题(VCCA 未连接到 A 侧电源,B 侧不会去耦电容器); 您能否提供有关这种与 I2C 总线中继器的错误连接如何可能影响 I2C 信号的见解?

我还计算了下拉最小值和最大值,它们在范围内,但我只是想知道下拉是否不够强。 有什么建议?

图表中是否还有其他突出的问题?

感谢你的帮助,

EE Yandrie Oyarzabal