“线程:测试”中讨论的其它部件,

您好,

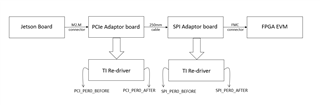

在我们的设计中,我们使用 Jetson NX 作为根组合体,使用 Arria 10 FPGA SoC 板作为端点配置。

PCIe 第2代,x2 (通道0和 lan1)的硬件配置(引导分段),中继器如下所示,

Equality=0x02,对于 FR4 10英寸跟踪,

de-Emphasis=-3.5dB,

VOD = 0.9V。

链路 稳定,板之间的通信正常。

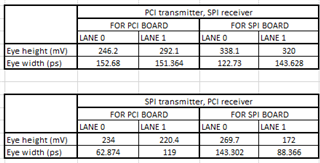

根据启动测试,在中继器 IC 之前和之后捕获的0号线(Jetson 套件正在传输且 FPGA 正在接收)的结果如下所示

在 PCI 板上,中继器 IC 之前:

在 PCI 板上,中继器 IC 之后:

在 SPI 板上,中继器 IC 之前:

在 SPI 板 上 ,中继器 IC 之后:

在两种情况下,如果通信被反转,并且在通道1上,我们也会获得类似的结果。

我想知道,如果捕捉到的眼图是不是预期的那样,为什么眼被凸起,而且在转发前更准确。 如果是,这种行为背后的技术原因是什么?

此外,如您在方框图中所见,我们有两个适配器板,即 PCIe 和 SPI,在 PCIe 板上的中继器和 SPI 板上的中继器之后,我们的眼睛行为不是相同的。

谢谢,

泽尔·沙阿