“线程: 测试”中讨论的其它部件

大家好,团队

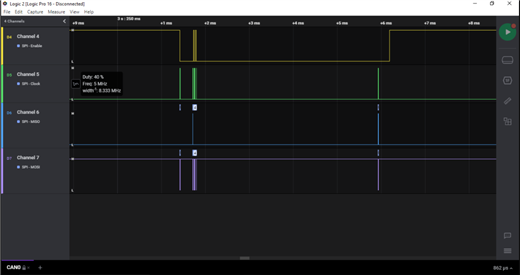

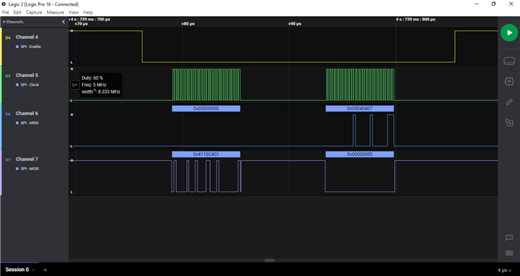

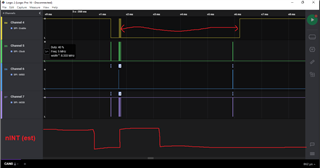

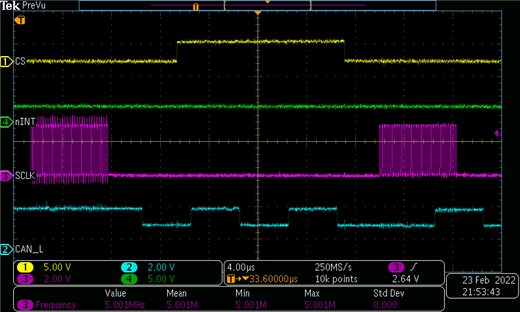

当我使用 tcan4x5x 驱动程序时,我正在连续执行发送 cansend 数据。 发送数据时,ifconfig 中 RX 字节的值将相应地递增。 在一定程度上,RX 数据包增量停止,并且无法接收和发送更多数据。 目前,驱动程序没有发出错误信息。

$ ifconfig

CAN0 链路接口:UNSPEC HWaddr 00-00-00-00-00-00-00-00-00-00-00-00-00-00-00-00-00-00

正在运行 NOARP MTU:16 公制:1.

Rx 数据包:65212错误:0丢弃:0溢出:0帧:0

Tx 数据包:65213错误:0丢弃:2溢出:0载波:2

冲突:0 txqueuelen:10.

Rx 字节:521696 (509.4 KiB) TX 字节:521704 (509.4 KiB)

中断:72

当我运行“ifconfig CAN0 down”并发送 cansend (CAN 初始化后)命令时,RX 数据包开始递增,并在一定时间后停止。

请帮我解决这个问题。

此致,

艾沙特