“线程”中讨论的其它部件:DP83869

您好,

我正在使用 DP83869 PHY 和 Artix 7 FPGA。 LAN 未与 PC 通信。 IC 配置为 MII 模式。 Tx 时钟仅有100mV 摆动。 详情如下。

-

DP83869在 MII 模式下使用。

-

使用的 VDDIO 电压为3.3V,IC 在2电源模式下使用。 未连接1.8V 电源。

-

MDIO 使用2.5k 欧姆电阻器被拉起

-

11k 偏置电阻器处的电压为1V

-

通电后,复位将保持在较低的状态201毫秒

-

然后,寄存器配置如下:

-

0x01DF0060

-

0x00005100 (10 Mbps MII 环回)

-

0x00105048

-

0x00090800

-

-

寄存器以34个时钟周期编写,第一位和最后一位为高阻抗。

-

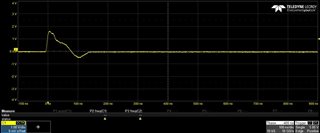

编程完成后,接收时钟的频率为2.5 MHz,具有3.3V (Pk-Pk)。 TX 时钟为2.5 MHz,但回转仅为100mV。

-

连接到 PC 时,链路无法通过。

-

在磁性输出处检查时,检测到10Base-Te Link Pulse。 还检测到自动协商 FLP。 所附链接脉冲和 FLP 的屏幕截图。

-

印刷电路板上使用的 LAN 连接器是圆形连接器,801-023-07M7-10SA (Mighty Mouse)。 LAN 电缆的一端具有圆形连接器的匹配连接器,而电缆的另一端是连接到 PC 的 RJ45连接器。 从圆形连接器到 RJ45的连接按照建议用于568B 的接线图进行。

PHY 电路图:

磁力原理图:

PHY Tx 时钟:

PHY Rx 时钟:

PHY 输出时钟:

链路脉冲:

自动内置 FLP:

请告诉我设计中是否缺少任何内容。

谢谢,此致,

沙夫纳