大家好,团队

我的客户想问两个问题。

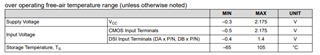

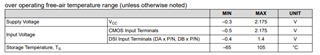

- DSI85 CLK 引脚可以使用2.5~3.3V 外部 SSXO 吗? 我看到最大电压是2.175。所以他们不能正确使用2.5V 到3.3V?

- 如果有任何频率分布的配置?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好,团队

我的客户想问两个问题。

杰森

参考时钟源由通过本地 I2C 接口编程的 HS_CLK_SRC (CSR 0x0A.0)选择。 如果选择了外部参考时钟,它将乘以 REFCLK_MULTIER (CSR 0x0B.1:0)中的因子,以生成 FlatLink LVDS 输出时钟。 选择外部参考时钟时,它必须在25 MHz 到154 MHz 之间。

如果选择了 DSI 信道 A 时钟,则生成 FlatLink LVDS 输出时钟时钟时,该时钟除以 DSI_CLK_DELAG( CSR 0x0B.7:3)中的因子。

此外,LVDS_CLK_RANGE (CSR 0x0A.3:1)和 CH_DSI_CLK_RANGE (CSR 0x12)必须 分别设置为 FlatLink LVDS 输出时钟和 DSI 通道 A 输入时钟的频率范围,内部 PLL 才能正常工作。 设定这些设置后,必须设置 PLL_EN (CSR 0x0D.0)以启用内部 PLL。

谢谢

大卫