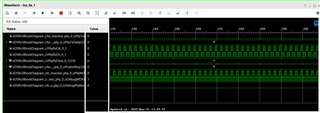

我有一种新设计,第一次使用DP8.3867万CR设备。 我在连接的另一端看到RxDV脉冲(较旧的PCB具有不同的phy),这是我不期望的。 换言之,在DP8.3867万CR上,我没有设置TxEn位以启动传输,但另一端似乎认为它正在接收传输。

在DP8.3867万上,我已清除BMCR寄存器中的自动协商位,并设置了我所需的速度(100 Mbps)。 如果我环回电缆,我会看到相应的RX时钟,因此我相信我的BMCR设置已被采用。 回送模式还显示RxDV通信,仅当我发送通信时(TxEN高)。

我还清除了CFG1中的所有位(我不确定这是否有必要,因为我不在1000Base-T模式下)。

此外,我们的设计没有在DP8.3867万CR上适当地绑定RxDV,因此我还进行了间接内存寻址以清除CFG4的位7。

这种设计基于FPGA,两端(带有DP8.3867万CR的新主板)和较旧的主板,意外流量导致试图处理此流量的旧主板出现问题。

我已经查看了我对MI的所有写入(BMCR,CFG1,CFG4的间接寻址),它们看起来是正确的,但由于设计是基于FPGA,因此很难读取状态寄存器来确认所有内容。

如果我错过了附加捆扎或配置寄存器设置,我们非常感谢您的任何想法!