请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:SN65HVD251 尊敬的:

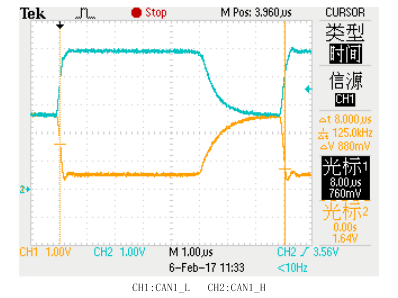

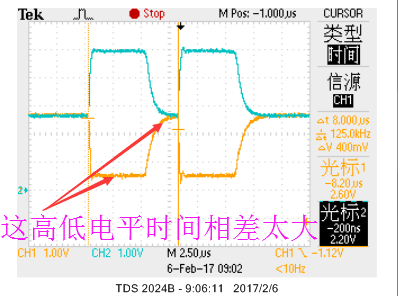

我们测试了SN65HVD251DR,发现高电平的时间是4.6 Us,低电平的时间是3.4 Us。 我们希望当频率为250 KHz,比特时间为4 us,高电平时间等于低电平时间时,比特时间的误差范围为0.2 % (传输数据时测试的10个电平的平均值)。 下一个波形是否正常? 您能否提供TI测试的SN65HVD251DR的波形? 如何调整参数以使高电平时间等于低电平时间?

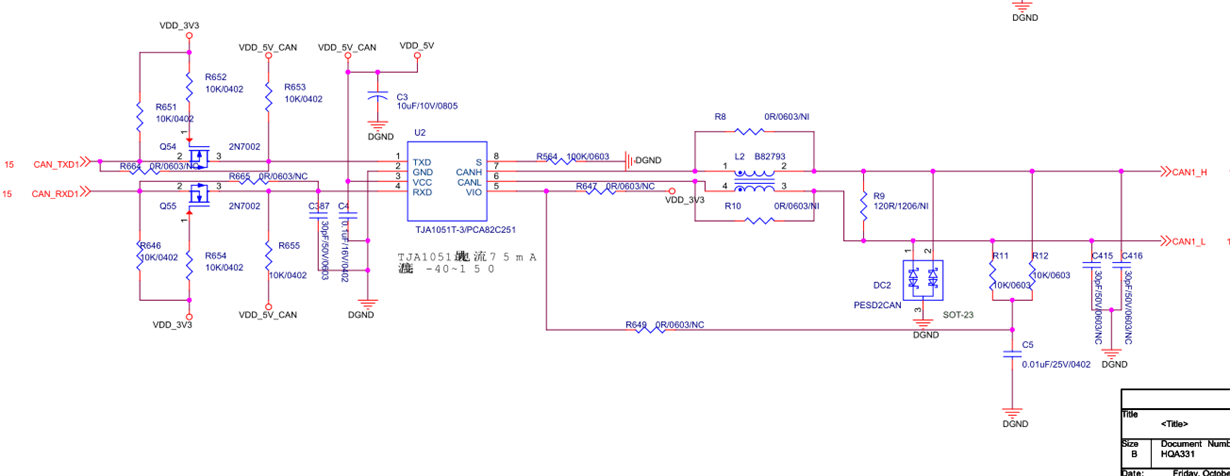

波形和原理图如下所示。 我正在等待您的回复,谢谢!