主题中讨论的其他部件: TLK106, DP8.3822万I

在我的设计中,我在RMII连接中使用TLK106L。

在主板和用于测试的个人计算机之间进行ping测试时,我有“不稳定”行为。

请注意,我在许多设计中都使用了TLK106L,没有任何问题。

我执行了很多测试来查找问题,(最后)它似乎TLK不能正常工作。

TLK和MAC的时钟源设计为数据表(SLLSEE3D–2013年8月–2016年4月修订)的图6-2。

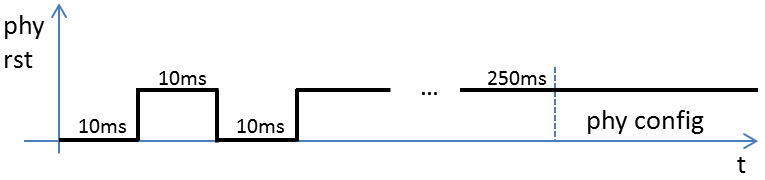

该问题与定时约束相关,第4.10 章节1通电定时,规格T2:“在VDD斜坡之前,XI时钟必须至少稳定1 µs。”

在我的设计TLK中,MAC和时钟振荡器共享相同的电源,因此不符合T2限制。

可能会发生什么?

感谢您的支持,此致。

Corrado