工具/软件:Linux

您好,

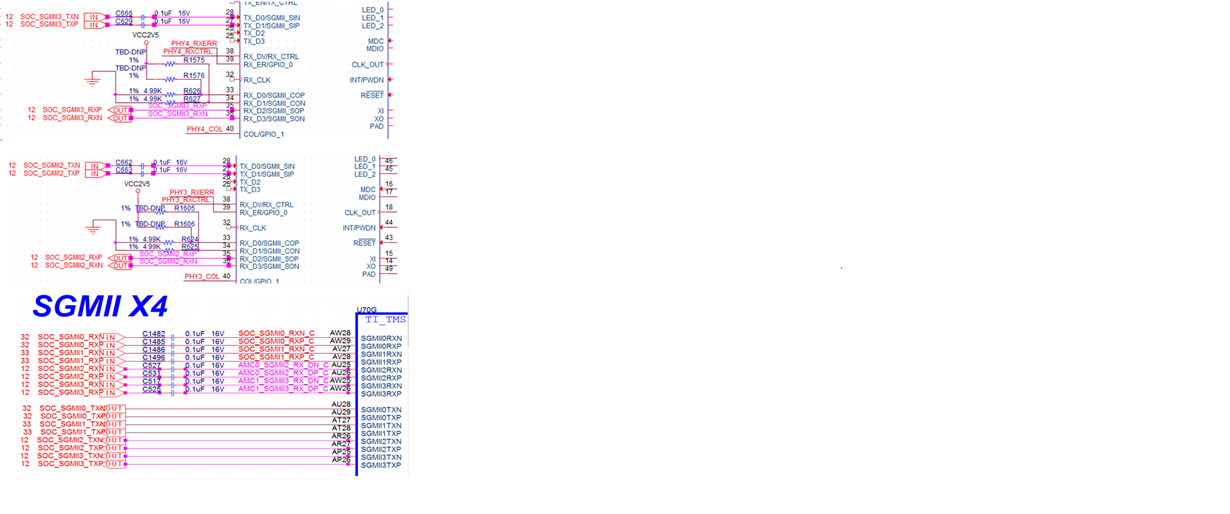

我们正在尝试在定制的k2hk主板中提供四个1Gig以太网端口。

->使用 SGMII接口的Marvell芯片的前两个以太网端口(eth0和eth1)。

状态: 工作中, 与k2hk EVM板中的一样

->使用SGMII接口的TI DP8.3867万的其它两个以太网端口(eth2和eth3)。

状态:显示接口,但无法ping。

启动TI DP8.3867万所遵循的步骤

在内核中

->由于mcsdk内核中没有dp8.3867万的驱动程序,我们从mcsdk移至Processor SDK 。

->我们在设备树,设备树的PFA中进行了更改。

->我们在dp8.3867万驱动程序中进行了更改,因为它仅支持RGMII模式,但我们需要 SGMII操作模式,修改后的驱动程序的PFA和原始驱动程序。

->与SGMII模式相关的修改是从启动加载程序文件ti.c (ti.c的PFA)中借用的

我们还尝试 了 PSDK Boot Loader

->已启用路径/driver/net/phi/ti.c中的ti.c,尝试ping其它IP,但系统重新启动。

请帮助我们完成此操作。

谢谢!

Gureesh Hirmath

高级设计工程师

Lekha无线解决方案

班加罗尔