主题中讨论的其他部件: THVD1550, THVD1500, SN65HVD3088E, SN65HVD82

它可能关注的人,

我们在J1708应用中使用SN6.5176万B芯片,如以下TI应用说明中的'J1708总线负载'部分所述:

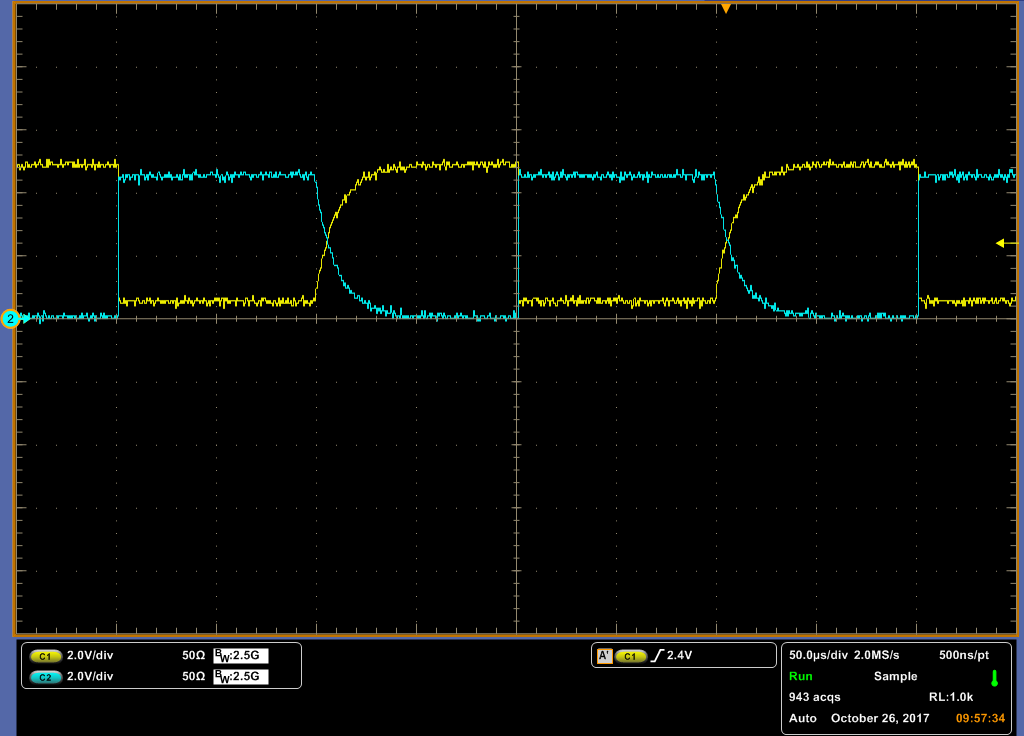

在测量信号时,我注意到禁用驱动器并依赖本应用手册中所述的端接时,端口A/B输出之间存在不平衡。 终结处理是对称的,但禁用驱动程序时,端口A的上升速度高于端口B的下降速度。

我从数据表中注意到,tPHZ和tPLZ延迟中的这些输出存在不平衡,最大值分别为250ns和30ns。 在此基础上,我有以下问题:

-即使输出端接是对称的,这种不平衡的延迟是否也与我看到的边缘速度不平衡有关?

->如果是,具体原因是什么?我们是否需要通过降低端口B上的下拉值(与端口A上的下拉值不同时)从外部补偿?

->如果是这种情况,您能否建议一些仍符合J1708规格的AM/FM干扰抑制要求的设备?

期待您的回复。

非常感谢,

Bhav