请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:SN75DP130 工具/软件:TI-RTOS

您好,先生

我有一个关于如何在SN75DP130上提高对问题的强调程度的问题吗?

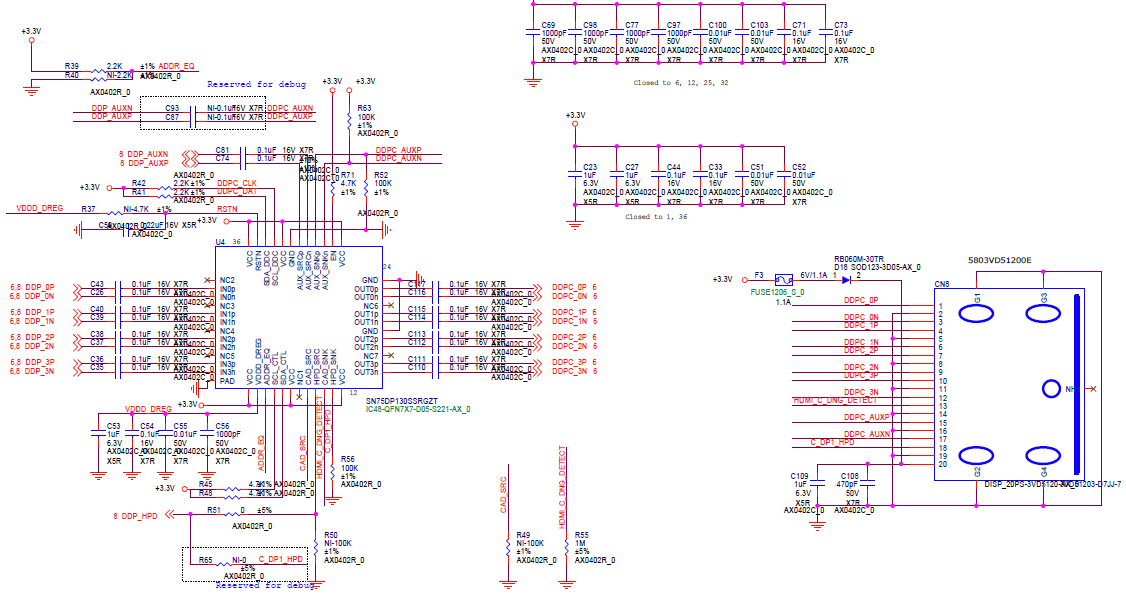

以下示意图和附件。 和布局跟踪,如下所示。

如果您有其他意见,请与我分享。 感谢您的大力支持。

| 对接板 | 主板 | ||||||||||||||||||

| 密耳 | 0.1 uf | 密耳 | PIN名称 | PIN名称 | 密耳 | 0.1 uf | 密耳 | 密耳 | 0欧姆 | 密耳 | PIN名称 | ||||||||

| DP连接 | 109.1 | C117 | 88.43 | OUT0_p | DP转子: SN75DP130SSRGZT |

IN0_p | 138.88 | C43. | 455.03 (途经:1) | 连接器 | 268.94 | SR35 | 3341.18 (途经:2) | DDI1_TXP[0] | CPU KabyLake |

||||

| 110.2 | C116 | 88.43 | OUT0_n | IN0_n | 138.96 | C26. | 454.43 (途经:1) | 269.08 | SR34. | 3339.30 (途经:2) | DDI1_TXN[0] | ||||||||

| 106.58 | C115 | 81.56 | 输出 | 输入1_p | 63.52 | C40 | 517.21 (途经:1) | 232.61 | SR33 | 3367.49 (途经:2) | DDI1_TXP[1] | ||||||||

| 105.25 | C114 | 82.65 | OUT1_n | IN1_n | 63.66 | C39. | 519.04 (途经:1) | 232.34 | SR32. | 3366.16 (途经:2) | DDI1_TXN[1] | ||||||||

| 109.87 | C113 | 81.13 | OUT2_p | in2_p | 66.13 | C38. | 405.34 (途经:1) | 216.78 | SR31. | 3393.70 (途经:2) | DDI1_TXP[2] | ||||||||

| 109.04 | C112 | 81.95 | OUT2_n | in2_n | 66.02 | C37. | 404.14 (途经:1) | 216.04 | SR30 | 3394.27 (途经:2) | DDI1_TXN[2] | ||||||||

| 114.67 | C111 | 87.73 | OUT3_p | in3_p | 68.59 | C36. | 475.87 (途经:1) | 229.71 | SR29. | 3596.13 (途经:2) | DDI1_TXP[3] | ||||||||

| 112.47 | C110 | 89 | OUT3_n | in3_n | 69.14 | C35. | 475.97 (途经:1) | 229.36 | SR28 | 3599.24 (途经:2) | DDI1_TXN[3] | ||||||||

| 密耳 | |||||||||||||||||||

| 1052.91 | Aux_SNKp | Aux_SRCp | 201.09 | C81. | 862.95 (途经:2,末节:29.76 mil) | 473.66 | R13. | 3407.88 (途经:2) | DDI1_AUXP | ||||||||||

| 1051.98 | AUX_SNKn | Aux_SRCn | 201.77 | C74. | 860.99 (途经:2,末节:29.36 mil) | 473.43 | R14 | 3409.11 (途经:2) | DDI1_AUXN | ||||||||||