请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:DS90LV001 尊敬的TI支持团队

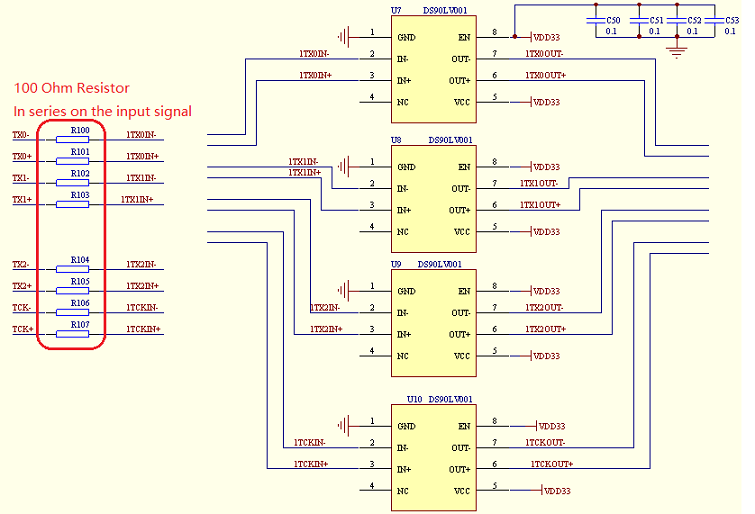

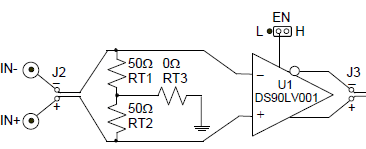

我们使用4pcs DS90LV001设计LVDS至TTL原理图。当我们对客户的系统(而不是EVM)进行样品测试时,我们发现输入信号上串联的一些电阻器 极有可能随机分解,但DS90LV001很好。电阻器的值为100欧姆,可以防止 LVDS异常断开。但我们 发现 DS90LV001参考设计上的不同连接,即IN+&IN-引脚分别将50欧姆电阻器连接到GND。

我的连接是否正确? 是否存在浪涌电流中断 串联电阻的风险? 如果 我的连接 正常,那么串联电阻器的适当值是多少?

客户‘s示意图:

DS90LV001 参考设计: