主题中讨论的其他部件:DP8.3869万

您好,TI专家

我们的客户想知道我需要配置DP8.3869万的芯片或寄存器以实现SYNP-E功能的哪种配置,它的恢复时钟输出引脚Rx_clk是吗? 它可以实现的频率同步精度是多少(标准偏差是多少)。

非常感谢!

此致,

威廉

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,TI专家

我们的客户想知道我需要配置DP8.3869万的芯片或寄存器以实现SYNP-E功能的哪种配置,它的恢复时钟输出引脚Rx_clk是吗? 它可以实现的频率同步精度是多少(标准偏差是多少)。

非常感谢!

此致,

威廉

您好William:

您可以使用以下方法对扩展寄存器进行编程

例如,您要编程(MMD,ADDR)=(1F,YYYY),数据= ZZZZ,然后编程

写入0x000D = 0x001F

写入0x000E = 0xYYYY

写入0x000D = 0x401F

写入0x000E = 0xZZZZ

例如,您要读取(MMD,ADDR)=(1F,YYYY)

写入0x000D = 0x001F

写入0x000E = 0xYYYY

写入0x000D = 0x401F

读取0x000E

您提到当您将设备更改为从属设备时没有明显的影响。 由于两个时钟都是25MHz,您看不到任何变化。 您是否测量了抖动以查看抖动配置文件是否发生了变化?

--

此致,

Gokul。

你好,Gokul。

我们的客户回复如下:

PS:连接到网络时,串行端口调试助手上将显示以下提示:

macb e000c000.ethernet eth0:无法生成目标频率:1.25亿 Hz

macb e000c000.ethernet eth0:链路连接(1000/Full)

IPv6:ADDRCONF (NETDEV_CHANGE):eth0:链路准备就绪

我不确定这是否会影响其恢复的时钟?

非常感谢!

此致,

Gokul。

你好,Gokul。

很抱歉,请忽略以上信息,我们的客户在下面回复:

PS:连接到网络时,串行端口调试助手上将显示以下提示:

macb e000c000.ethernet eth0:无法生成目标频率:1.25亿 Hz

macb e000c000.ethernet eth0:链路连接(1000/Full)

IPv6:ADDRCONF (NETDEV_CHANGE):eth0:链路准备就绪

我不确定这是否会影响其恢复的时钟?

非常感谢!

此致,

威廉

你好,Gokul。

是的,我需要获取SyncE时钟作为IEEE1588时钟同步硬件时间戳的标记;根据另一个问题和答案,我已经解决了CLK_OUT端口生成125MHz时钟的问题。

根据您的描述,有两种方法可获得SyncE时钟:1. CLK_OUT端口恢复时钟;2. RX_CLK恢复时钟,但需要将模式更改为MDI从属模式。

我暂时不能尝试第一种方法,因为我没有跟踪集来将时钟带到我的主板上;我尝试了第二种方法,但没有得到我想要的结果;并将主控设置为手动MDIX; 从属设备在设置为手动MDI后,它们之间的数据包丢失率会上升。

在这个阶段,我正在重新设计板,以便将从CLK_OUT获得的时钟引入板;我想从您那里得到的帮助是:1. 如何正确配置第二种获取SyncE恢复时钟的方法? 2.通过DP8.3869万恢复的SyncE时钟可实现哪种频率同步准确性?

感谢您的回答!

此致,

威廉

您好 Gokul

是的,我需要获取SyncE时钟作为IEEE1588时钟同步硬件时间戳的标记;根据另一个问题和答案,我已经解决了CLK_OUT端口生成125MHz时钟的问题。

根据您的描述,有两种方法可获得SyncE时钟:1. CLK_OUT端口恢复时钟;2. RX_CLK恢复时钟,但需要将模式更改为MDI从属模式。

我暂时不能尝试第一种方法,因为我没有跟踪集来将时钟带到我的主板上;我尝试了第二种方法,但没有得到我想要的结果;并将主控设置为手动MDIX; 从属设备在设置为手动MDI后,它们之间的数据包丢失率会上升。

在这个阶段,我正在重新设计板,以便将从CLK_OUT获得的时钟引入板;我想从您那里得到的帮助是:1. 如何正确配置第二种获取SyncE恢复时钟的方法? 2.通过DP8.3869万恢复的SyncE时钟可实现哪种频率同步准确性?

感谢您的回答!

此致,

威廉

您好,William:

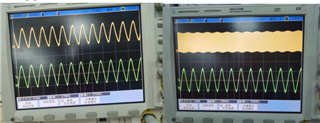

根据我的理解,您正在测量发射/恢复时钟或板-1与板-2的恢复/同步时钟之间的延迟。

当电缆连接在它们之间并且电路板连接在一起时,所有频率都将对齐,因此您会看到固定的延迟。

断开电缆连接时,不会对齐1号板和2号板的时钟。 这是由于两块板之间的频率不匹配。 任何较小的频率偏移都将使时钟看起来与肉眼不同步。

因此,总的来说,我认为您能够观察到系统中的目标。

--

此致,

Gokul。