主题中讨论的其他部件: DP8.3822万I

您好,

我正在尝试使用DP83TD510E和DP8.3822万I制作10BASE-T1L至10BASE-T介质转换器电路。 我制造了原型。 RGMII无法将数据从822传送到510。 RGMII将数据从510精细地传递到822。 流量测试仪报告CRC和定位错误。

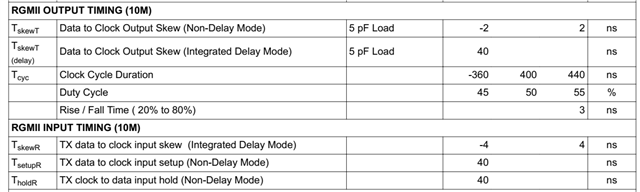

DP83TD510E 没有RGMII的时序图。 查看 DP8.3822万I的计时图,我想知道问题是否是822 RX_CLK连接没有转换到510 TX_CLK连接。 2个部件的数据表指明了这一点

- DP8.3822万I 没有向RX_CLK添加班次,但向TX_CLK添加了班次。

- DP83TD510E NO SHIFT添加到RX_CLK或TX_CLK。

板上没有微控制器来发送MDIO命令。 PHY通过绑带进行配置。 以下是绑带的配置方式。

DP8.3822万I :

| 销钉 | 针脚编号 | 内部 | 设置为 | 说明 |

| 名称 | PU/PD | 模式 | ||

| -------------------------------------------------------------------------------------------------------------------------------------------------------- | ||||

| 列 | 29. | PU | 4. | Internal PU (内部PU)-禁用100BASE-FX,将PHY addr设置为0.0001万。 |

| RX_D0 | 30. | PD | 二 | 外部10K PU和2.49K PD -将10BASE-Te,半/全双工和PHY地址设置为0.0001万。 |

| RX_D1 | 31. | PD | 1. | Internal PD (内部PD)-禁用EEE,将PHY地址设置为0.0001万。 |

| RX_D2 | 32岁 | PD | 1. | Internal PD (内部PD)-禁用Fast Link Drop (快速链路断开),将PHY地址设置为0.0001万。 |

| RX_D3 | 1. | PD | 1. | Internal PD (内部PD)-将10BASE-Te,半/全双工和PHY地址设置为0.0001万。 |

| LED_0 | 17. | PU | 4. | 内部PU -设置10BASE-Te,半/全双工。 |

| CRS | 27. | PU | 1. | 外部1.96K PD -将LED_0配置为链路和活动。 |

| Rx_ER | 28. | PU | 3. | 外部1.96K PD,6.2K PU -启用Auto-MDIX,启用RGMII。 |

| RX_DV | 26. | PD | 1. | 内部PD -使用XI引脚处提供的25MHz参考时钟设置RGMII模式。 |

DP83TD510E:

| 带子 | 销钉 | 针脚编号 | 内部 | 说明 |

| # | 名称 | PU/PD | ||

| -------------------------------------------------------------------------------------------------------------------------------------------------------- | ||||

| 1. | RX_D3 | 13. | PD | Internal PD (内部PD)-将PHY地址设置为0000。 |

| 二 | RX_D2 | 14. | PD | 内部PD -将引脚18设置为CRS_DV。 |

| 3. | RX_D1 | 15. | PD | Internal PD (内部PD)-将PHY设置为RGMII模式。 |

| 4. | RX_D0 | 16. | PD | Internal PD (内部PD)-将PHY地址设置为0000。 |

| 5. | RX_DV | 18. | PD | 内部PD -将Clock/LED_1引脚设置为25MHz时钟输出。 |

| 6. | RE_ERR | 20. | PD | Internal PD (内部PD)-将PHY地址设置为0000。 |

| 7. | LED_2 | 28. | PD | External PU (外部PU)-将APL TX/RX电压级别设置为首选1 Vpp。 |

| 8. | LED_0 | 29. | PD | External PU (外部PU)-将PHY设置为RGMII模式。 |

| 9. | GPIO1 | 32岁 | PD | Internal PD (内部PD)-将PHY地址设置为0000。 |

| 10. | GPIO2 | 8. | 不适用 | 强制PD -将收件人的轻触设置为50 Ω。 |

我不确定问题是什么。 延迟只是一个猜测。 如果你对什么可能是错误以及如何弄清楚它是什么以及如何解决它有任何想法,我很乐意听到他们的想法。

谢谢