主题中讨论的其他部件:Alp.

我最初在下面的主题中发布了以下评论,但被要求制作一个新主题。 某些语法引用了上一个线程。

我在使用DS90UB954和DS90UB953链路时遇到了非常类似的问题。

我还不能确定为什么会发生这种情况,但它与地址或注册偏移无关。

我不知道您的部件的默认BCC超时是什么,但在954/953设置中,它是254毫秒。

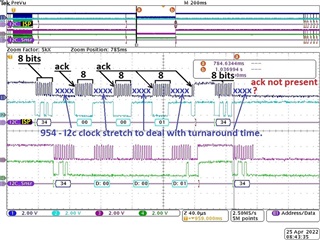

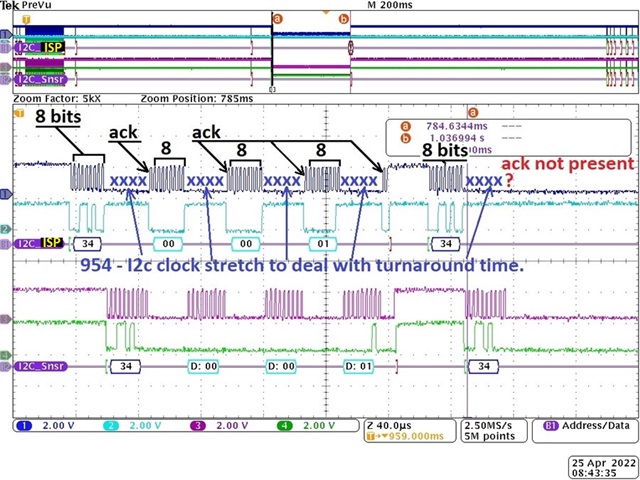

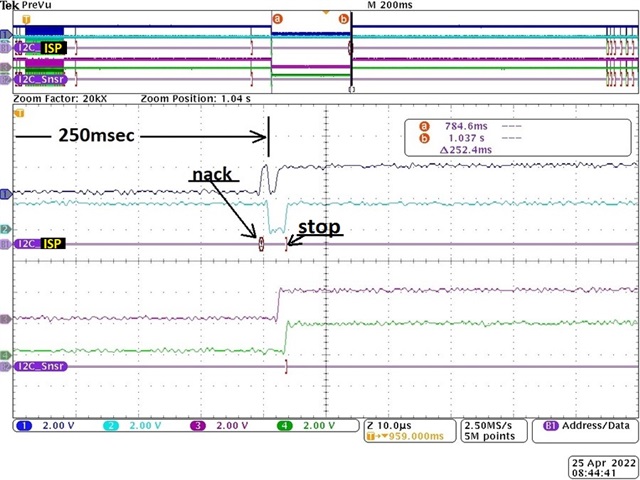

初始示波器捕获的上半部分显示成功启动过程的ISP至954波形。 同一图像的底部显示了一个故障波形,其中954没有产生ISP I2C写入传感器的确认。 点A和点B之间的时间大约为250ms,这是954 BCC超时的默认值。

下一个范围捕获显示写入失败开始的特写(捕获上部的A点)。 您可以看到由7位(写入)地址,16位寄存器偏移和8位数据组成的良好写入周期。 对于每个8位周期,您会看到在等待953和传感器完成时钟拉伸后出现的插孔。 在下一个4字节写入周期的地址部分中,954不会向ISP生成所需的ack,但您可以看到,该ack是由传感器“生成”到953的。

最终范围捕获显示同一失败写入周期结束时的特写(捕获上部的b点)。 当BCC超时时时,954的正常过程是发出nack,然后允许主中继器发出停止循环。 这正是捕获中看到的内容。

我还不能确定为什么会发生这种情况,但它与地址或注册偏移无关。

我不知道您的部件的默认BCC超时是什么,但在954/953设置中,它是254毫秒。

您可以看到所需的信号协议在写入过程中正常工作,但它无法从954返回到ISP。

Justin,我将在下面的另一个主题中重新输入您的最后一条评论,这样我就可以添加我的答案,而不会丢失。

*******************************

您好,David:

在FPD链路设备中,当A Master从Master->DES->SER.-> Slave发送I2C命令时,目标Slave需要通过SER和DES之间的电缆链路将ACK响应发回给Master。

DRC:您可以在波形中看到目标从属设备在所有情况下都"完成"了953。

8位I2C地址首先发送到从属设备。 如果从机以正确的ACK响应,则主机将发送另一个8位消息,即实际的读/写命令。 在我看来,当I2C消息从主机->从属设备发送时,使用了错误的地址,并且没有与地址匹配的从属设备。 因此,任何从属设备都不会向主设备发送ACK响应,而主设备也不会发送8位I2C读/写命令。 如果没有发回ACK位,SER上的监视计时器将在一段时间后自动取消I2C操作。

DRC:我相信你会看到7位地址和写入位从主中继器到954,通过同轴电缆,从953到图像传感器,图像传感器正确地响应了ACK。 在地址后面,您还会看到16位寄存器偏移,然后是要写入的8位数据。 所有4个周期都显示图像传感器产生所需的图像堆叠。

DRC:针对您的描述,我有以下内容-如果主中继器向总线上不存在的地址发出写入,数据线将会很高(因为下拉),主中继器仍将能够生成其时钟 (因为没有Slave (从属)来保持时钟线低),这将产生一个nack。 这是正常的I2C周期,表示从属地址不存在,并且"不会"产生BCC超时。

下面还有一些应用说明,用于描述包括FPD-Link设备时的主题:

最佳,

Justin Phan

***********

我愿意听取关于这一失败的原因的任何想法。

谢谢!

David