Other Parts Discussed in Thread: TLK106

主题中讨论的其他部件: DP8.3822万H, DP8.3825万I

晚上好,

在高温下启动时,我们遇到一些TLK106 PHY问题。 我们有多个主板,每个主板都安装了7个PHY,在50C的温度下开机时,PHY的平均故障率为10 15 %。 其余的85 90 % 没有问题,即使在高达90C的环境温度下进行电源循环也是如此。 问题PHY将在45°C左右正常启动,并在至少90°C时正常运行,没有任何问题。 但是,如果我们重启主板,问题PHY将无法启动。

症状似乎与 https://e2e.ti.com/support/interface-group/interface/f/interface-forum/53.2984万/tlk105-tlk106-in-ethercat-network-doesn-t-start-at-temperatures-over-35-c非常相似, 但我们的设计有一些明显的差异。

设计细节:

- 7 x TLK106 PHY

- Xilinx Zynq SOC中实例化的Mac

- AVDD = VDD_IO = 3.3V

- RMII模式

- XI = 50MHz,3.3V,由Zynq生成

- 每个MAC和PHY之间的单个MDIO连接

50MHz参考时钟由Zynq可编程逻辑生成。 在PHY通电后,Zynq在不到5毫秒的时间内出现,但将可编程逻辑加载/配置到FPGA中需要1700毫秒以上(是的,1.7 秒)。 因此,直到PHY内部POR被取消断言大约1.7 秒后,XI中的参考时钟才稳定。 当1.5 操作系统启动时,在XI稳定后,我们再按住\reset low ~秒。

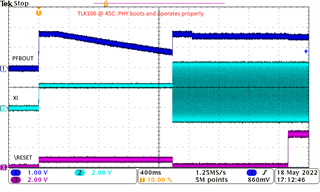

在出现问题的PHY上,我们看到PFBOUT 1.55V电源开始线性衰减,在通电后大约250ms开始。 线性衰减的斜率似乎与环境温度直接相关;温度越高,斜率越大。 如果在XI启动时PFBOUT仅降至0.70V左右,则PFBOUT将重置为1.55V,PHY将恢复(请参阅第一示波器画面)。 但是,如果PFPBOUT进一步下降(由于温度斜率较高或XI启动进一步延迟),PFPBOUT将保持低位,PHY将无响应(请参阅第二示波器画面)。 注意陡坡。

一旦没有响应,通过MDIO声明\RESET或写入PFB_OFF都不能恢复PHY (看起来1.55V为内部寄存器供电,因此MDIO已死机)。

在工作PHY上,我们不会看到任何PFPBOUT衰减,功率循环高达90C。

问题:

- AVDD加电后/加电前,XI在XMS内是否有稳定的要求? 我在数据表中看不到任何此类计时要求。 注:我能够通过黑客攻击一个PHY来延迟AVDD,以便在通电之前时钟保持稳定。 有了这种攻击,问题PHY就能正常启动。

- 是否知道为什么此行为仅出现在某些(样本大小为10 15 %) PHY上? 我无法从我们的主板中推断出相关性;在一个主板上,PHY1和PHY7有问题,而在另一个主板上,PHY2有问题。 这似乎是随机的,PHYs会容忍这种情况。 所有使用中的PHY均来自同一批次/卷。

- 考虑到我的设计的限制条件(XI在AVDD之后是1.7秒),是否有任何解决方法? 断言\reset不起作用。

- 如果理解了这种行为,TI是否有机会筛查在我的应用中工作的部件?

提前感谢您的帮助。 请原谅我的镜头不够完美。 XI输入实际上是0-3.3V,但考虑到在一个小腔室中环境温度为60C的问题,我糟糕的接地连接导致50MHz时钟的电压测量不准确。

-Kyle,BSEE航空电子设计