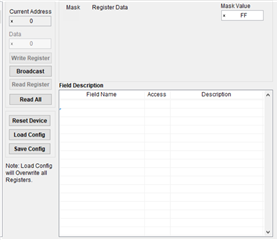

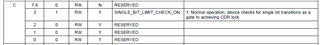

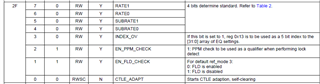

0x0 Shared Registers_0x00 00 0x1 Shared Registers_0x01 D1 0x2 Shared Registers_0x02 00 0x3 Shared Registers_0x03 00 0x4 Shared Registers_0x04 01 0x5 Shared Registers_0x05 10 0x6 Shared Registers_0x06 00 0x7 Shared Registers_0x07 04 0xFF Global Registers_0xFF 00 0x0 Channel 0_0x00 00 0x1 Channel 0_0x01 00 0x2 Channel 0_0x02 04 0x3 Channel 0_0x03 A5 0x4 Channel 0_0x04 00 0x5 Channel 0_0x05 00 0x6 Channel 0_0x06 00 0x7 Channel 0_0x07 00 0x8 Channel 0_0x08 00 0x9 Channel 0_0x09 00 0xA Channel 0_0x0A 10 0xB Channel 0_0x0B 0F 0xC Channel 0_0x0C 08 0xD Channel 0_0x0D 00 0xE Channel 0_0x0E 93 0xF Channel 0_0x0F 69 0x10 Channel 0_0x10 3A 0x11 Channel 0_0x11 E0 0x12 Channel 0_0x12 A0 0x13 Channel 0_0x13 30 0x14 Channel 0_0x14 00 0x15 Channel 0_0x15 52 0x16 Channel 0_0x16 7A 0x17 Channel 0_0x17 36 0x18 Channel 0_0x18 40 0x19 Channel 0_0x19 23 0x1A Channel 0_0x1A 00 0x1B Channel 0_0x1B 03 0x1C Channel 0_0x1C 24 0x1D Channel 0_0x1D 00 0x1E Channel 0_0x1E 21 0x1F Channel 0_0x1F 55 0x20 Channel 0_0x20 00 0x21 Channel 0_0x21 00 0x22 Channel 0_0x22 00 0x23 Channel 0_0x23 C0 0x24 Channel 0_0x24 40 0x25 Channel 0_0x25 00 0x26 Channel 0_0x26 00 0x27 Channel 0_0x27 00 0x28 Channel 0_0x28 00 0x29 Channel 0_0x29 00 0x2A Channel 0_0x2A 30 0x2B Channel 0_0x2B 00 0x2C Channel 0_0x2C 72 0x2D Channel 0_0x2D 82 0x2E Channel 0_0x2E 00 0x2F Channel 0_0x2F F6 0x30 Channel 0_0x30 00 0x31 Channel 0_0x31 40 0x32 Channel 0_0x32 11 0x33 Channel 0_0x33 88 0x34 Channel 0_0x34 BF 0x35 Channel 0_0x35 1F 0x36 Channel 0_0x36 31 0x37 Channel 0_0x37 00 0x38 Channel 0_0x38 00 0x39 Channel 0_0x39 00 0x3A Channel 0_0x3A A5 0x3B Channel 0_0x3B 00 0x3C Channel 0_0x3C 00 0x3D Channel 0_0x3D 00 0x3E Channel 0_0x3E 80 0x3F Channel 0_0x3F 00 0x40 Channel 0_0x40 00 0x41 Channel 0_0x41 01 0x42 Channel 0_0x42 04 0x43 Channel 0_0x43 10 0x44 Channel 0_0x44 40 0x45 Channel 0_0x45 08 0x46 Channel 0_0x46 02 0x47 Channel 0_0x47 80 0x48 Channel 0_0x48 03 0x49 Channel 0_0x49 0C 0x4A Channel 0_0x4A 30 0x4B Channel 0_0x4B 41 0x4C Channel 0_0x4C 50 0x4D Channel 0_0x4D C0 0x4E Channel 0_0x4E 60 0x4F Channel 0_0x4F 90 0x50 Channel 0_0x50 88 0x51 Channel 0_0x51 82 0x52 Channel 0_0x52 A0 0x53 Channel 0_0x53 46 0x54 Channel 0_0x54 52 0x55 Channel 0_0x55 8C 0x56 Channel 0_0x56 B0 0x57 Channel 0_0x57 C8 0x58 Channel 0_0x58 57 0x59 Channel 0_0x59 5D 0x5A Channel 0_0x5A 69 0x5B Channel 0_0x5B 75 0x5C Channel 0_0x5C D5 0x5D Channel 0_0x5D 99 0x5E Channel 0_0x5E 96 0x5F Channel 0_0x5F A5 0x60 Channel 0_0x60 00 0x61 Channel 0_0x61 00 0x62 Channel 0_0x62 00 0x63 Channel 0_0x63 00 0x64 Channel 0_0x64 00 0x65 Channel 0_0x65 00 0x66 Channel 0_0x66 00 0x67 Channel 0_0x67 20 0x68 Channel 0_0x68 00 0x69 Channel 0_0x69 0A 0x6A Channel 0_0x6A 44 0x6B Channel 0_0x6B 00 0x6C Channel 0_0x6C 00 0x6D Channel 0_0x6D 00 0x6E Channel 0_0x6E 00 0x6F Channel 0_0x6F 00 0x70 Channel 0_0x70 03 0x71 Channel 0_0x71 20 0x72 Channel 0_0x72 00 0x73 Channel 0_0x73 00 0x74 Channel 0_0x74 00 0x75 Channel 0_0x75 00 0x0 Channel 1_0x00 00 0x1 Channel 1_0x01 00 0x2 Channel 1_0x02 00 0x3 Channel 1_0x03 A5 0x4 Channel 1_0x04 00 0x5 Channel 1_0x05 00 0x6 Channel 1_0x06 00 0x7 Channel 1_0x07 00 0x8 Channel 1_0x08 00 0x9 Channel 1_0x09 00 0xA Channel 1_0x0A 10 0xB Channel 1_0x0B 0F 0xC Channel 1_0x0C 08 0xD Channel 1_0x0D 00 0xE Channel 1_0x0E 93 0xF Channel 1_0x0F 69 0x10 Channel 1_0x10 3A 0x11 Channel 1_0x11 E0 0x12 Channel 1_0x12 A0 0x13 Channel 1_0x13 30 0x14 Channel 1_0x14 00 0x15 Channel 1_0x15 52 0x16 Channel 1_0x16 7A 0x17 Channel 1_0x17 36 0x18 Channel 1_0x18 40 0x19 Channel 1_0x19 23 0x1A Channel 1_0x1A 00 0x1B Channel 1_0x1B 03 0x1C Channel 1_0x1C 24 0x1D Channel 1_0x1D 00 0x1E Channel 1_0x1E 21 0x1F Channel 1_0x1F 55 0x20 Channel 1_0x20 00 0x21 Channel 1_0x21 00 0x22 Channel 1_0x22 00 0x23 Channel 1_0x23 C0 0x24 Channel 1_0x24 44 0x25 Channel 1_0x25 00 0x26 Channel 1_0x26 00 0x27 Channel 1_0x27 00 0x28 Channel 1_0x28 00 0x29 Channel 1_0x29 00 0x2A Channel 1_0x2A 30 0x2B Channel 1_0x2B 00 0x2C Channel 1_0x2C 72 0x2D Channel 1_0x2D 82 0x2E Channel 1_0x2E 00 0x2F Channel 1_0x2F F6 0x30 Channel 1_0x30 00 0x31 Channel 1_0x31 40 0x32 Channel 1_0x32 11 0x33 Channel 1_0x33 88 0x34 Channel 1_0x34 BF 0x35 Channel 1_0x35 1F 0x36 Channel 1_0x36 31 0x37 Channel 1_0x37 00 0x38 Channel 1_0x38 00 0x39 Channel 1_0x39 00 0x3A Channel 1_0x3A A5 0x3B Channel 1_0x3B 00 0x3C Channel 1_0x3C 00 0x3D Channel 1_0x3D 00 0x3E Channel 1_0x3E 80 0x3F Channel 1_0x3F 00 0x40 Channel 1_0x40 00 0x41 Channel 1_0x41 01 0x42 Channel 1_0x42 04 0x43 Channel 1_0x43 10 0x44 Channel 1_0x44 40 0x45 Channel 1_0x45 08 0x46 Channel 1_0x46 02 0x47 Channel 1_0x47 80 0x48 Channel 1_0x48 03 0x49 Channel 1_0x49 0C 0x4A Channel 1_0x4A 30 0x4B Channel 1_0x4B 41 0x4C Channel 1_0x4C 50 0x4D Channel 1_0x4D C0 0x4E Channel 1_0x4E 60 0x4F Channel 1_0x4F 90 0x50 Channel 1_0x50 88 0x51 Channel 1_0x51 82 0x52 Channel 1_0x52 A0 0x53 Channel 1_0x53 46 0x54 Channel 1_0x54 52 0x55 Channel 1_0x55 8C 0x56 Channel 1_0x56 B0 0x57 Channel 1_0x57 C8 0x58 Channel 1_0x58 57 0x59 Channel 1_0x59 5D 0x5A Channel 1_0x5A 69 0x5B Channel 1_0x5B 75 0x5C Channel 1_0x5C D5 0x5D Channel 1_0x5D 99 0x5E Channel 1_0x5E 96 0x5F Channel 1_0x5F A5 0x60 Channel 1_0x60 00 0x61 Channel 1_0x61 00 0x62 Channel 1_0x62 00 0x63 Channel 1_0x63 00 0x64 Channel 1_0x64 00 0x65 Channel 1_0x65 00 0x66 Channel 1_0x66 00 0x67 Channel 1_0x67 20 0x68 Channel 1_0x68 00 0x69 Channel 1_0x69 0A 0x6A Channel 1_0x6A 44 0x6B Channel 1_0x6B 00 0x6C Channel 1_0x6C 00 0x6D Channel 1_0x6D 00 0x6E Channel 1_0x6E 00 0x6F Channel 1_0x6F 00 0x70 Channel 1_0x70 03 0x71 Channel 1_0x71 20 0x72 Channel 1_0x72 00 0x73 Channel 1_0x73 00 0x74 Channel 1_0x74 00 0x75 Channel 1_0x75 00 0x0 Channel 2_0x00 00 0x1 Channel 2_0x01 00 0x2 Channel 2_0x02 00 0x3 Channel 2_0x03 A5 0x4 Channel 2_0x04 00 0x5 Channel 2_0x05 00 0x6 Channel 2_0x06 00 0x7 Channel 2_0x07 00 0x8 Channel 2_0x08 00 0x9 Channel 2_0x09 00 0xA Channel 2_0x0A 10 0xB Channel 2_0x0B 0F 0xC Channel 2_0x0C 08 0xD Channel 2_0x0D 00 0xE Channel 2_0x0E 93 0xF Channel 2_0x0F 69 0x10 Channel 2_0x10 3A 0x11 Channel 2_0x11 E0 0x12 Channel 2_0x12 A0 0x13 Channel 2_0x13 30 0x14 Channel 2_0x14 00 0x15 Channel 2_0x15 52 0x16 Channel 2_0x16 7A 0x17 Channel 2_0x17 36 0x18 Channel 2_0x18 40 0x19 Channel 2_0x19 23 0x1A Channel 2_0x1A 00 0x1B Channel 2_0x1B 03 0x1C Channel 2_0x1C 24 0x1D Channel 2_0x1D 00 0x1E Channel 2_0x1E 21 0x1F Channel 2_0x1F 55 0x20 Channel 2_0x20 00 0x21 Channel 2_0x21 00 0x22 Channel 2_0x22 00 0x23 Channel 2_0x23 C0 0x24 Channel 2_0x24 44 0x25 Channel 2_0x25 00 0x26 Channel 2_0x26 00 0x27 Channel 2_0x27 00 0x28 Channel 2_0x28 00 0x29 Channel 2_0x29 00 0x2A Channel 2_0x2A 30 0x2B Channel 2_0x2B 00 0x2C Channel 2_0x2C 72 0x2D Channel 2_0x2D 82 0x2E Channel 2_0x2E 00 0x2F Channel 2_0x2F F6 0x30 Channel 2_0x30 00 0x31 Channel 2_0x31 40 0x32 Channel 2_0x32 11 0x33 Channel 2_0x33 88 0x34 Channel 2_0x34 BF 0x35 Channel 2_0x35 1F 0x36 Channel 2_0x36 31 0x37 Channel 2_0x37 00 0x38 Channel 2_0x38 00 0x39 Channel 2_0x39 00 0x3A Channel 2_0x3A A5 0x3B Channel 2_0x3B 00 0x3C Channel 2_0x3C 00 0x3D Channel 2_0x3D 00 0x3E Channel 2_0x3E 80 0x3F Channel 2_0x3F 00 0x40 Channel 2_0x40 00 0x41 Channel 2_0x41 01 0x42 Channel 2_0x42 04 0x43 Channel 2_0x43 10 0x44 Channel 2_0x44 40 0x45 Channel 2_0x45 08 0x46 Channel 2_0x46 02 0x47 Channel 2_0x47 80 0x48 Channel 2_0x48 03 0x49 Channel 2_0x49 0C 0x4A Channel 2_0x4A 30 0x4B Channel 2_0x4B 41 0x4C Channel 2_0x4C 50 0x4D Channel 2_0x4D C0 0x4E Channel 2_0x4E 60 0x4F Channel 2_0x4F 90 0x50 Channel 2_0x50 88 0x51 Channel 2_0x51 82 0x52 Channel 2_0x52 A0 0x53 Channel 2_0x53 46 0x54 Channel 2_0x54 52 0x55 Channel 2_0x55 8C 0x56 Channel 2_0x56 B0 0x57 Channel 2_0x57 C8 0x58 Channel 2_0x58 57 0x59 Channel 2_0x59 5D 0x5A Channel 2_0x5A 69 0x5B Channel 2_0x5B 75 0x5C Channel 2_0x5C D5 0x5D Channel 2_0x5D 99 0x5E Channel 2_0x5E 96 0x5F Channel 2_0x5F A5 0x60 Channel 2_0x60 00 0x61 Channel 2_0x61 00 0x62 Channel 2_0x62 00 0x63 Channel 2_0x63 00 0x64 Channel 2_0x64 00 0x65 Channel 2_0x65 00 0x66 Channel 2_0x66 00 0x67 Channel 2_0x67 20 0x68 Channel 2_0x68 00 0x69 Channel 2_0x69 0A 0x6A Channel 2_0x6A 44 0x6B Channel 2_0x6B 00 0x6C Channel 2_0x6C 00 0x6D Channel 2_0x6D 00 0x6E Channel 2_0x6E 00 0x6F Channel 2_0x6F 00 0x70 Channel 2_0x70 03 0x71 Channel 2_0x71 20 0x72 Channel 2_0x72 00 0x73 Channel 2_0x73 00 0x74 Channel 2_0x74 00 0x75 Channel 2_0x75 00 0x0 Channel 3_0x00 00 0x1 Channel 3_0x01 00 0x2 Channel 3_0x02 04 0x3 Channel 3_0x03 57 0x4 Channel 3_0x04 00 0x5 Channel 3_0x05 00 0x6 Channel 3_0x06 00 0x7 Channel 3_0x07 00 0x8 Channel 3_0x08 00 0x9 Channel 3_0x09 00 0xA Channel 3_0x0A 10 0xB Channel 3_0x0B 0F 0xC Channel 3_0x0C 08 0xD Channel 3_0x0D 00 0xE Channel 3_0x0E 93 0xF Channel 3_0x0F 69 0x10 Channel 3_0x10 3A 0x11 Channel 3_0x11 E0 0x12 Channel 3_0x12 A0 0x13 Channel 3_0x13 30 0x14 Channel 3_0x14 00 0x15 Channel 3_0x15 52 0x16 Channel 3_0x16 7A 0x17 Channel 3_0x17 36 0x18 Channel 3_0x18 40 0x19 Channel 3_0x19 23 0x1A Channel 3_0x1A 00 0x1B Channel 3_0x1B 03 0x1C Channel 3_0x1C 24 0x1D Channel 3_0x1D 00 0x1E Channel 3_0x1E 21 0x1F Channel 3_0x1F 55 0x20 Channel 3_0x20 00 0x21 Channel 3_0x21 00 0x22 Channel 3_0x22 00 0x23 Channel 3_0x23 C0 0x24 Channel 3_0x24 44 0x25 Channel 3_0x25 00 0x26 Channel 3_0x26 00 0x27 Channel 3_0x27 00 0x28 Channel 3_0x28 00 0x29 Channel 3_0x29 00 0x2A Channel 3_0x2A 30 0x2B Channel 3_0x2B 00 0x2C Channel 3_0x2C 72 0x2D Channel 3_0x2D 82 0x2E Channel 3_0x2E 00 0x2F Channel 3_0x2F F6 0x30 Channel 3_0x30 00 0x31 Channel 3_0x31 40 0x32 Channel 3_0x32 11 0x33 Channel 3_0x33 88 0x34 Channel 3_0x34 BF 0x35 Channel 3_0x35 1F 0x36 Channel 3_0x36 31 0x37 Channel 3_0x37 1D 0x38 Channel 3_0x38 00 0x39 Channel 3_0x39 00 0x3A Channel 3_0x3A A5 0x3B Channel 3_0x3B 00 0x3C Channel 3_0x3C 00 0x3D Channel 3_0x3D 00 0x3E Channel 3_0x3E 80 0x3F Channel 3_0x3F 00 0x40 Channel 3_0x40 00 0x41 Channel 3_0x41 01 0x42 Channel 3_0x42 04 0x43 Channel 3_0x43 10 0x44 Channel 3_0x44 40 0x45 Channel 3_0x45 08 0x46 Channel 3_0x46 02 0x47 Channel 3_0x47 80 0x48 Channel 3_0x48 03 0x49 Channel 3_0x49 0C 0x4A Channel 3_0x4A 30 0x4B Channel 3_0x4B 41 0x4C Channel 3_0x4C 50 0x4D Channel 3_0x4D C0 0x4E Channel 3_0x4E 60 0x4F Channel 3_0x4F 90 0x50 Channel 3_0x50 88 0x51 Channel 3_0x51 82 0x52 Channel 3_0x52 A0 0x53 Channel 3_0x53 46 0x54 Channel 3_0x54 52 0x55 Channel 3_0x55 8C 0x56 Channel 3_0x56 B0 0x57 Channel 3_0x57 C8 0x58 Channel 3_0x58 57 0x59 Channel 3_0x59 5D 0x5A Channel 3_0x5A 69 0x5B Channel 3_0x5B 75 0x5C Channel 3_0x5C D5 0x5D Channel 3_0x5D 99 0x5E Channel 3_0x5E 96 0x5F Channel 3_0x5F A5 0x60 Channel 3_0x60 00 0x61 Channel 3_0x61 00 0x62 Channel 3_0x62 00 0x63 Channel 3_0x63 00 0x64 Channel 3_0x64 00 0x65 Channel 3_0x65 00 0x66 Channel 3_0x66 00 0x67 Channel 3_0x67 20 0x68 Channel 3_0x68 00 0x69 Channel 3_0x69 0A 0x6A Channel 3_0x6A 44 0x6B Channel 3_0x6B 00 0x6C Channel 3_0x6C 00 0x6D Channel 3_0x6D 00 0x6E Channel 3_0x6E 00 0x6F Channel 3_0x6F 00 0x70 Channel 3_0x70 03 0x71 Channel 3_0x71 20 0x72 Channel 3_0x72 00 0x73 Channel 3_0x73 00 0x74 Channel 3_0x74 00 0x75 Channel 3_0x75 00