主题中讨论的其他器件: TIC12400-Q1

尊敬的团队:

这是来自 TI 韩国的 Chris、我的一位客户正在经历开关 IC ESD 测试期间发生的错误。 我详细解释了目前的情况、可能的原因和问题。

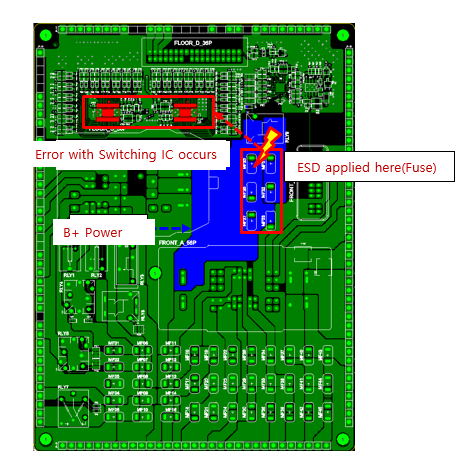

问题:如下图所示,当空气放电+15kV (ICU 通电)被应用于 ICU 保险丝时,开关 IC 不工作。 (不适用于输入开关)。

※开关 IC:TIC10024-Q1

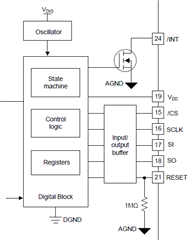

可能的原因: 当应用 ESD 时,噪声可能会应用于开关 IC 中的数字块,并且硬件复位引脚已被触发。

情况 - 1)开关 IC 停止工作后、电池复位后、它再次正常工作。

2) 2)应用 ESD 后、寄存器设置在开关 IC 上复位。

3) 3)当 ESD 直接施加到开关 IC 的输入端时、工作正常。

4) 4)增大开关输入端的电阻和电容不能解决问题。

正在进行的过程:当 SPI 通信线路上的串行电阻值从100欧姆增加到390欧姆时,问题就会得到解决。

→ 如果 ICU 功能评估和 SPI 波形没有问题、将选择此解决方案来解决该问题。

→电阻器增加到390欧姆后、ICU 功能评估没有问题。

4.问题 :1) SPI 通信线路中可能出现的噪声是否会重置 IC 的寄存器设置? (或触发硬件复位引脚)?

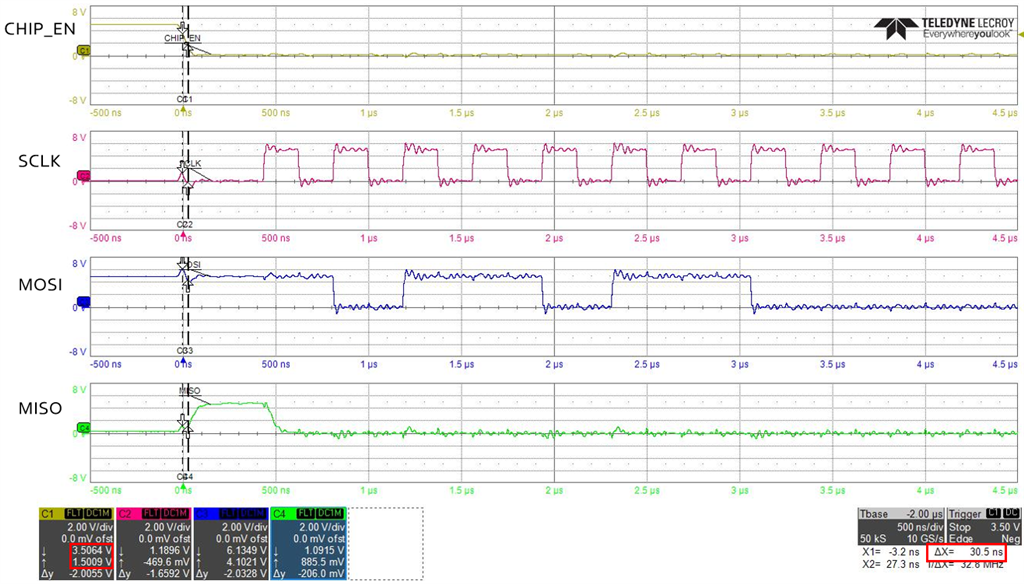

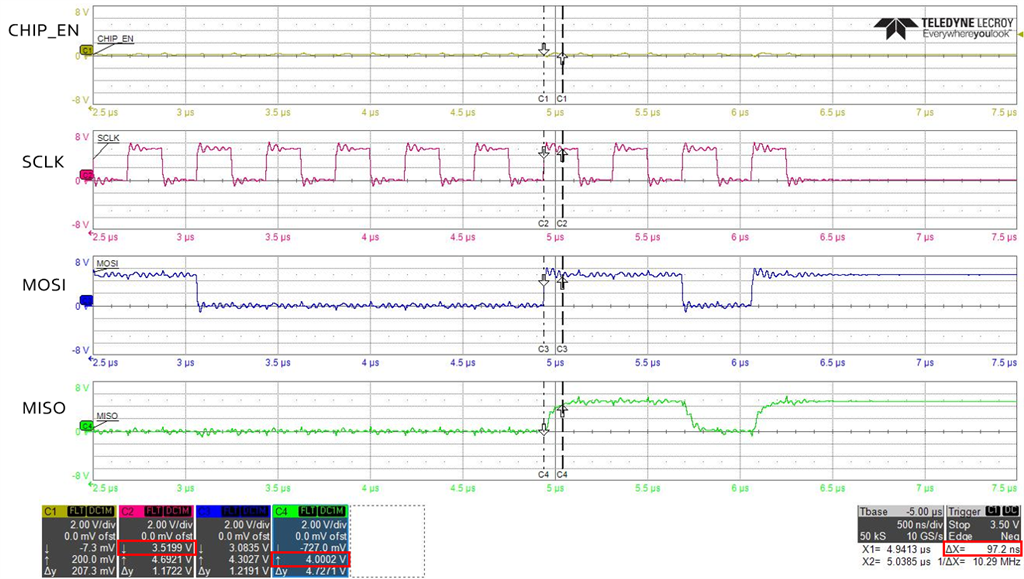

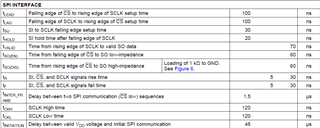

2) 2)回顾了带有390 Ω 串行电阻器的 SPI 波形后、大多数值都符合数据表上的 SPI 时序参数、但一些参数超出了数据表上的 SPI 时序参数。 是否可能存在功能或性能问题? (请参阅下面的波形)。

- T_F_CS = 30.5ns

- t_VALID = 97.2ns

3) 3)硬件复位引脚中的触发器之外、出现此问题还有其他可能的原因吗?

4) 4)读取时序(开关 IC 读取 MOSI 信号)和读取时序(MCU 读取 MISO)是否适合 SCLK 的下降沿?