主题中讨论的其他器件: DP83869

我们有一个用于新设计的电路板、但它在1G 时不通过 MII 环回。 某些消息通过 OK、但其他消息包含错误。 在错误消息中、我们观察到 RX 时钟从125MHz 增加到大约140MHz。 在正常消息中、RX 时钟保持在125MHz。 有什么想法可以导致这种情况? 是否有任何关于如何解决的建议?

我们在使用 DP83867的早期设计板和具有 DP83869HM 的其他项目板上运行了环回软件。 在这两种情况下、回送工作正常、没有错误。

谢谢、

Ron

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我们有一个用于新设计的电路板、但它在1G 时不通过 MII 环回。 某些消息通过 OK、但其他消息包含错误。 在错误消息中、我们观察到 RX 时钟从125MHz 增加到大约140MHz。 在正常消息中、RX 时钟保持在125MHz。 有什么想法可以导致这种情况? 是否有任何关于如何解决的建议?

我们在使用 DP83867的早期设计板和具有 DP83869HM 的其他项目板上运行了环回软件。 在这两种情况下、回送工作正常、没有错误。

谢谢、

Ron

您好 Ron Curtis

感谢您的查询。

我是否可以假设您引用的 RX 与 PHY 有关。

RX 时钟取决于时钟源。 您能否在用于 PHY 的时钟源上提供更多输入?

您能否探测 PHY 的 clock_out 以检查时钟是否有任何变化。

您提到过您能够在另一个 DP83869设计上运行回送模式。 根据输入、我们可以首先假设 寄存器配置正常。

此致、

Sreenivasa

是的、通过 RX 时钟、我们将探测 PHY 上的引脚32 RX_CLK。

此设计中的时钟源是引脚19和20上的25MHz 晶体。 我们对 CLK_OUT 进行了探测、是的、我们在将以下任一内容写入寄存器0x0170 "0x3 =通道 D 接收时钟"或"0xD (未记录参考时钟)"中的 CLK_O_SEL 时看到时钟增加

当 0xC =基准时钟(与 XI 输入时钟同步)时、它没有增加。

我在 https://training.ti.com/sites/default/files/docs/ti_precision_labs_-_ethernet_anatomy_of_the_phy.pdf 的第5页看到 、RX_CLK 似乎是"恢复的 CLK"和"本地 REF_CLK"的组合。

Sreenivasa、

感谢快速响应。 当0xD 写入寄存器0x170中的 CLK_O_SEL 时、您是否有关于 CLK_OUT 的任何其他信息? 我们之所以这样做、是因为在不同的线程中出现了响应。 我们看不到数据表中定义的此0xD 值。

是的、通过 RX 时钟、我们将探测 PHY 上的引脚32 RX_CLK。

此设计中的时钟源是引脚19和20上的25MHz 晶体。 我们对 CLK_OUT 进行了探测、是的、我们在将以下任一内容写入寄存器0x0170 "0x3 =通道 D 接收时钟"或"0xD (未记录参考时钟)"中的 CLK_O_SEL 时看到时钟增加

当 0xC =基准时钟(与 XI 输入时钟同步)时、它没有增加。

我在 https://training.ti.com/sites/default/files/docs/ti_precision_labs_-_ethernet_anatomy_of_the_phy.pdf 的第5页看到 、RX_CLK 似乎是"恢复的 CLK"和"本地 REF_CLK"的组合。

如果需要、以下内容提供了寄存器的配置:

GEN_CTRL 寄存器(0x001F)报告0x0000

GEN_CTRL 寄存器(0x001F)写入0x8000

BMCR 寄存器(0x0000)报告0x1140

BMCR 寄存器(0x0000)写入0x0140

RGMII_CTRL 寄存器(0x0032)写入0x00D0

BMCR 寄存器(0x0000)报告0x0140

BMCR 寄存器(0x0000)写入0x4140

IO_MUX_CFG 寄存器(0x0170)报告0x0C0F

IO_MUX_CFG 寄存器(0x0170)写入0x0D0F

IO_MUX_CFG 寄存器(0x0170)报告0x0D0F

机密寄存器(0x00C6)写入0x0010

GEN_CTRL 寄存器(0x001F)报告0x0000

GEN_CTRL 寄存器(0x001F)写入0x4000

报告0xA802的 PHY_STATUS 寄存器(0x0011)

您好 Ron Curtis

感谢您的参与。

不建议将0x0170寄存器设置作为环回测试的一部分。 这仍然是默认值。

由于 MII 环回测试 MAC 和 PHY 之间的接口、因此不需要 RJ45电缆连接。

回送说明:

近端环回

近端回送提供了通过数字或模拟电路将传输的数据回路到接收器的功能。 信号环回的点是使用环回控制位选择的、并提供多个选项。

配置环回模式时、环回配置寄存器(LOOPCR)、地址0x00FE、应该被设定为0xE720。

为了保持所需的运行模式、在选择近端回送模式之前、应禁用自协商。

此约束不适用于外部环回模式。 在选择近端回送模式之前、应禁用自动 MDIX。 MDI 或 MDIX 配置应手动配置。

MII 环回

MII 环回是通过 PHY 的最允许的环路。 这是一种用于验证 MAC 和 PHY 之间的通信的测试模式。 在 MII 环回模式下、数据会环回、并可通过寄存器配置为向媒体传输数据。

使用 BMCR (寄存器地址0x0000)配置 MII 环回。

在100Base-TX 模式中、通过寄存器0x00启用 MII 环回后、需要将0x0004写入寄存器0x16、以便 MII 环回正常运行。

有关配置环回模式的信息、请参阅以下文档(这与 DP8389类似)

https://www.ti.com/lit/an/snla246a/snla246a.pdf

我将总结一般遵循的步骤

GEN_CTRL 寄存器(0x001F)写入0x8000

BMCR 寄存器(0x0000)写入0x1140

延迟控制

请使用0x32和0x86配置所需的延迟

环回配置寄存器(LOOPCR)、地址0x00FE、 写入0xE720。

GEN_CTRL 寄存器(0x001F)写入0x4000

此致、

Sreenivasa

您好 Ron Curtis

另一个问题。 以下配置的来源是什么- TI 是否提供了这些配置?

如果需要、以下内容提供了寄存器的配置:

GEN_CTRL 寄存器(0x001F)报告0x0000

GEN_CTRL 寄存器(0x001F)写入0x8000

BMCR 寄存器(0x0000)报告0x1140

BMCR 寄存器(0x0000)写入0x0140

RGMII_CTRL 寄存器(0x0032)写入0x00D0

BMCR 寄存器(0x0000)报告0x0140

BMCR 寄存器(0x0000)写入0x4140

IO_MUX_CFG 寄存器(0x0170)报告0x0C0F

IO_MUX_CFG 寄存器(0x0170)写入0x0D0F

IO_MUX_CFG 寄存器(0x0170)报告0x0D0F

机密寄存器(0x00C6)写入0x0010

GEN_CTRL 寄存器(0x001F)报告0x0000

GEN_CTRL 寄存器(0x001F)写入0x4000

报告0xA802的 PHY_STATUS 寄存器(0x0011)

此致、

Sreenivasa

您好 Ron Curtis

在寄存器访问方面、我有一个简单的注释、不过您可能会关注这些内容。 请务必遵循扩展寄存器访问9.4.9.1扩展地址空间访问部分。

此致、

Sreenivasa

您好、Sreenivasa、

感谢您提供更多信息。 我意识到我没有回答您关于寄存器配置来源的问题。 我们从用于 DP83867的 Xilinx 驱动程序开始、然后进行了修改以包含 TI 的 DP83867故障排除指南中的步骤、然后添加了其他调试仪表。 我们还尝试使用 LOOPCR 而不是 BMCR 来进行其他环回、但决定将重点放在通过 BMCR 编程的 MII 环回上、而不是 LOOPCR。

因此、我们在周末取得了突破。 我们已经发现移除晶体并替换为函数发生器、然后电路板通过1G 的 MII 环回测试。 根据 DP93969HM 数据表、我们已经为 CL1和 CL2尝试了36pF 电容器、这是 ABM3内部负载电容18pF 的负载电容的2倍。 我们还尝试了18pF。 它在25MHz 时两种频率下均会按预期振荡、但当我们尝试传输数据时、似乎会在几个时钟周期内升至27MHz。 有人建议我们应该做些什么不同? 我们当前未使用 R1。 在这种情况下、它会产生什么影响吗?

谢谢、

Ron

您好、Sreenivasa、

感谢您的快速响应。 在数据表的第105页、R1位于 PHY 上的 XO 引脚和 C2之间。 我们目前没有使用它。 此外、在我们的设计中、晶体上有一个1M 欧姆的电阻器、我不知道设计人员为什么添加了它。 您以前是否见过这种情况? 我们今天的计划是将其移除并查看电路板的性能。 我们将探测 CLKOUT 以了解结果。

什么是"带帽"? 数据表中是否讨论了"寄生电容"?

谢谢、

Ron

您好、Sreenivasa、

晶体尽可能靠近、电路板上有通孔过孔。 我没有精确的布线长度、如果需要、我可以得到。 使用的布局与之前使用 DP83867的电路板上使用的布局相同。 它在该板上工作。 由于数据表中的写操作发生了变化、我想 DP83869 PHY 内部发生了一些变化。 由于 XI/XO 引脚在 DP83867和 DP83869之间移动、此电路板上的布线略长。

您好 Ron、

感谢您的参与。 DP83869振荡器已有改进。

如果我理解正确、没有回路、您就看不到晶体频率 发生变化-理解 正确吗?

电源的更多信息、

VDDA2P5 (2.5V)

VDDA1P8_1 -开路或1.8V (开路时、两个引脚不应短接)

VDDIO - 1.8V o 3.3V

VDD1P1 - 1.1V

在 DP83867中、VDD1P1为1V。

您能不能检查所有引脚是否都有100nF + 1uF 的电容、是否每个电源轨都有10nF + 10uF 的电容。

此致、

Sreenivasa

我今天将检查每个电压电平。 之前、我们看了去耦电容器。 它们不像我想看到的那样靠近引脚。 作为故障排除步骤的一部分、我们使用一些通孔过孔在更靠近的位置添加了额外的去耦电容器。 当我们使用函数发生器时、这些额外的电容器位于电路板上。 有人告诉我、原始电容器尽可能靠近所有需要路由信号的通孔。 您是否知道是否可以将869与通孔通孔配合使用、或者电路板是否应该使用盲孔来使盖子更靠近?

我没有确切的器件型号、但它是 abm3、 https://abracon.com/Resonators/abm3.pdf。 它是18pF 的标准负载电容、我没有现成的 temp/freq 容差/freq 稳定性等标识符、但如果需要、我可以得到。 我认为、如果内存正常工作、则是30ppm。 它是25MHz。

您好、Sreenivasa、

电压正确、我对"10nF + 10uF for each supply rail "有疑问。 该板上每个869 PHY 有四个。 每个电源轨都有自己的层。 如果这些电容器与较大的电容器组合在一起、是否正常? 我看到1.8V 有5个22uF、3个2.2uF 和11个0.1uF; 1.1有1个22uF、1个0.1uF 和 2.5有1个22uF 和1个0.1uF。 除了靠近每个 PHY 引脚的引脚的引脚外、这些引脚还包括:

我意识到这些并不完全是数据表中列出的值、但我被告知在之前的电路板上使用了它们、每个867 PHY 有四个、没有问题。 我建议如果完成另一个电路板布局、那么我们应该使用数据表中的值。 此外、我建议将电容器放置在更靠近引脚的位置、目前这些电容器在每个 PHY 的底部被分组在一起。 我正在尝试确定我们可以做些什么来使该板正常工作。 当我们移除晶体振荡器电路并通过 FPGA 的25MHz 输出驱动 XI 时、它似乎适用于两个 PHY。 计划在其他两个 PHY 上尝试类似的操作。 您认为这种方法有什么问题吗?

谢谢、

Ron

您好 Ron、

感谢您的测量。 VDDIO 是您使用的是1.8V 还是3.3V。

关于晶体、我不需要确切的器件型号。 请注意、如果晶振为4引脚类型、有时客户倾向于将信号路由到晶振内部 、建议 避免这种情况。

对于分度、 必须分别处理每个器件和每个引脚、以便进行100nF + 1uF 去耦。

对于10nF + 10uF、每个器件都必须被视为单独的电源轨。

它们更靠近 每个器件。

您是否为2个 PHY 提供了通用时钟。 最好使用具有缓冲器的单个时钟输出。

需要时钟输出以满足 DP83869要求。

在 DP83869复位释放之前、时钟应处于活动状态。

此致、

Sreenivasa

您好、Sreenivasa、

我询问了在早期采取类似方法的问题、并考虑到冗余、我做出了一些倒退。 当时、我想使用其中一个的 CLK_OUT 来驱动下一个、这将节省成本、因为其他3个 PHY 不需要晶体。 担心的是、如果一个电压下降、那么所有电压都会下降。

我们为什么不能让869 PHY 与晶振一起工作、这仍然是一个谜、但当我们使用函数发生器而不是晶体时、这种方法很好。 该类似的晶体电路在867上工作。 您是否会提供有关869内部 XI/XO 电路改进的更多详细信息?

谢谢、

Ron

您好 Ron、

感谢你的答复。

无论 IO 电压如何、DP83867时钟输入范围均限制为1.8V。 当使用外部振荡 器且 IO 为3.3V 时、这需要一个时钟分频器。 我们不需要使用带有 DP83869的电容分压器。

是否可以共享晶体布局。 您是否有机会尝试使用一些替代晶体来排除特定的晶体问题?

我不确定是否缺少输入、您是否测量了时钟输出、是否看到频率变化?

此致、

Sreenivasa

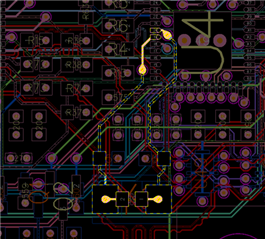

我们使用869的电路板布局如下、使用867的布局类似。 布局的唯一区别是 XI/XO 引脚(14/15与19/20) 位置。 在867上、布线长度短~75mil。

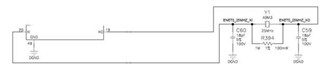

原理图如下。 它使用867。 使用869时不起作用、我们尝试了18pF 到33pF 范围内的电容器。 我们还移除了1Mohm 电阻器。 我们还尝试了不同的晶体、并在多个 PHY 上进行了测试。

我们配置了 CLK_OUT 并查看了输出。 当配置为输出25MHz 时,我们看不到该位移。 但是、当 CLK_OUT 配置为输出125MHz 时、我们确实会看到传输数据时的频率变化(MII 环回)。

同样、我们的去耦电容器在此布局上的位置不是最佳选择。 但是、在其中一个 PHY 上、我们已死区在非常靠近引脚的位置安装了额外的电容器。 当我们使用函数发生器替换晶体时、PHY 在使用或不使用附加电容器的情况下工作。 使用晶体时 、我们会收到大约40%的错误消息。 错误消息具有频移、正常消息没有频移。

感谢您的帮助和支持、帮助我们寻找根本原因、

Ron

Sreenivasa 您好、

晶振和1M 欧姆电阻位于底部的焊盘上。 上面是两个电容器(数据表图110中的 CL1和 CL2)的四个焊盘。 上面的6个焊盘是 1.1V 的去耦电容器。 一侧连接到接地平面、另一侧连接到1.1V 平面。 上面是 R575、它连接在接地端和 PHY 上的引脚12 (RBIAS)之间。 R575上方是 R13、MDIO 的电压上拉至1.8V (PHY 上的引脚41)。 靠近右侧迹线顶部的是 PHY (布局上的 U4)下连接到接地的三个过孔。 U4上“U”开头的过孔连接到 PHY 上的引脚9,连接到2.5V 平面。

这是否能回答您的问题? 作为故障排除步骤的一个步骤、我需要向团队核实是否添加了串联电阻(以及使用的值)。 目前还没有。 您会为串联电阻器推荐什么值?

谢谢、

Ron

您好、Sreenivasa、

PHY 具有一个向 XI 提供25MHz 时钟的函数发生器、可同时通过 MII 环回并发送和接收 UDP 数据包。 我们在电路板上添加了一条白线、并对 FPGA 进行了重新编程、以允许 FPGA 的输出为 XI 提供25MHz 时钟 我们发现这允许 MII 回送通过、但它不会自动协商以允许发送 UDP 数据包。 在此配置中、在25MHz 时钟可用之前通电。 我们已经尝试在25MHz 时钟启动后进行硬件复位、但 PHY 仍然不会自动协商。 有什么建议吗?

谢谢、

Ron

您好、Sreenivasa、

我们在上周五测量并确认 XI 输入符合上表中的规格。 我们昨天在 电压电平方面进行了发现。 事实上、当我们对 FPGA 进行1.8伏输出编程时、它的输出电压为2.5V、超过了 IX 输入的最高高电平电压。 我们正在努力纠正这种情况。 这是否会导致回送通过、但自动协商失败?

我们仍然不明白为什么按照我们的原始设计使用晶体会失败。 按照晶振制造商的建议、我们在晶振输入上串联了一个电位计。 这导致 PHY 不再通过环回测试、但仍能在 LED 上看到活动。 我们在该板上还有3个其他 PHY、一个连接到函数发生器、一个连接到 FPGA、另一个仍在我们的原始设计配置中使用晶体。

Ron

您好 Ron、

感谢您的参与。

MDI 接口需要精确的时钟、因为该时钟是数据传输的参考时钟。 在施加2.5V 时钟且 VDDIO 为1.8V 的情况下、我假设时钟失真、从而导致 MDI 接口错误。

由于 RGMII 上的环回具有时钟基准、因此偏差是时钟不会影响性能。

很抱歉再次问您, 您是否有机会将负载电容器移至靠近晶体的位置(使用1M 焊盘)并执行一些测试。

此致、

Sreenivasa

您好、Sreenivasa、

感谢您的回答。 我们已经按照前面讨论的方法创建了移动负载电容器的工作说明、但等待技术人员进行更新。 明天将有一个可用。 很难同时进行虚拟和焊接。 :-) 同时,我们决定将连接的一个 PHY 的函数发生器电压增加到2.5V,以查看我们在较高电压下是否会发生故障。 事实证明、它继续在我们尝试的一个 PHY 上工作。 在上一个故障排除步骤中、我们还添加了额外的去耦电容器、即 PHY。 我正在考虑在没有额外去耦电容器的 PHY 上重复此测试、但这需要有人焊接导线。

867和869之间的引脚排列不同。 否则、我们不会执行新的电路板旋转。 867板到869板的更改旨在适应引脚分配的变化。

是的、所有四个板载器件都具有相似的布局。

感谢您在我们继续努力解决此问题时提供的帮助。

此致、

Ron