您好!

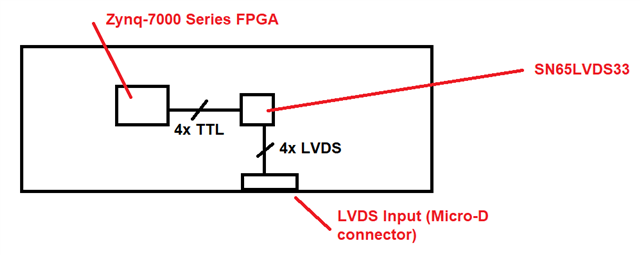

我们 使用 SN65LVDS33来发送4个 LVDS 信号:CLK、D0、D1和 D2。

CLK 以100MHz 的频率运行。

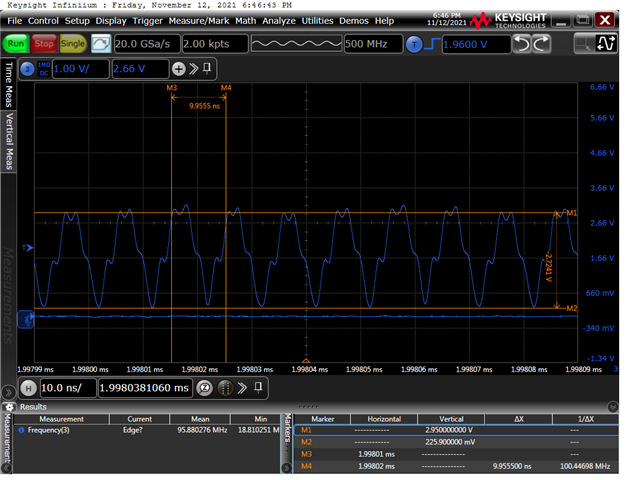

当3个数据通道中的任何2个被启用时(例如 D0和 D1、或者 D0和 D2、或者 D1和 D2)、接收器输出(即、单端侧)上的 CLK 信号完整性(SI)是令人满意的。

当启用所有3个数据通道(即 D0、D1和 D2)时、随着传输的数据模式中增加更多信号边沿、单端信号的 CLK SI 会下降、并会变差。 输入侧(即 LVDS 侧)的 CLK SI 保持良好。

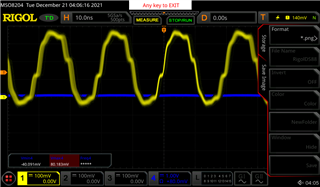

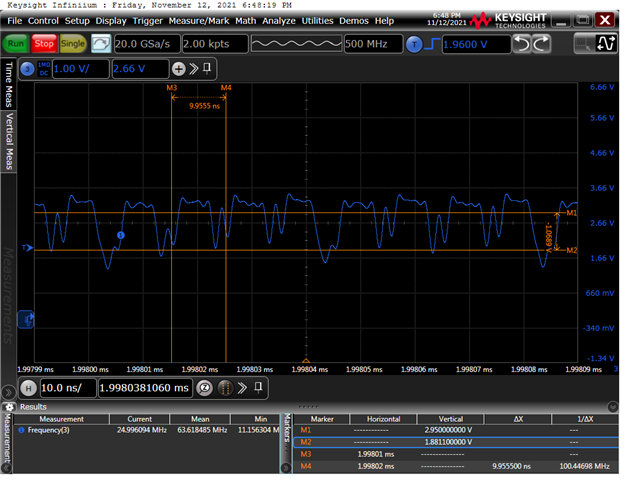

例如、如果在所有通道上传输的数据模式为0x2222 (请参阅左侧的下图)或0x4444 (请参阅右侧的下图)、 则 CLK SI 良好。

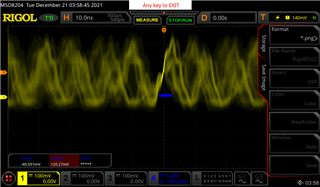

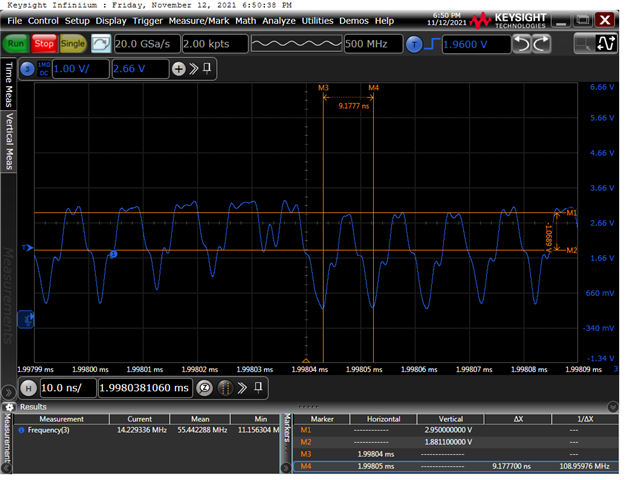

如果向数据模式添加了更多的信号边沿、例如0xA9A9、CLK SI 会下降到 错过某些周期的程度。 请参见下图。

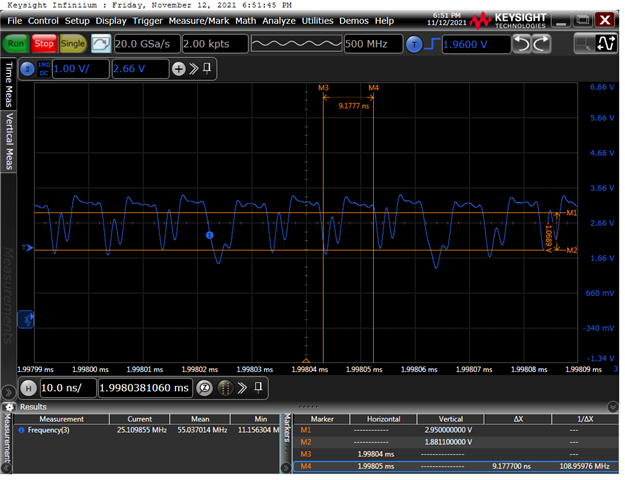

如果传输位不断变化的数据模式、例如0x5555 (左侧下方的图像)或0xAAAA (右侧下方的图像)、CLK 停止摆动至0V 并变得不可用。

我们是否推动 SN65LVDS33芯片超越其功能?

LVDS 端的所有信号都正常。 布线使用正确的阻抗进行布线、但其长度比 TI 应用手册中有关 LVDS 信号的建议更长。

请注意、如果我们以50MHz 而不是100MHz 运行 CLK、则 CLK SI 在所有情况下都保持良好。

如有任何反馈和/或建议、我们将不胜感激。

谢谢、

Aki